Recently, I encountered the same error and created some tests to investigate the problem. It turned out that the OBUFT inference in submodules works in some cases. The tests below use the synth_xilinx command for synthesis (I split the synth_xilinx command into few parts, to obtain the diagrams before the iopadmap call)

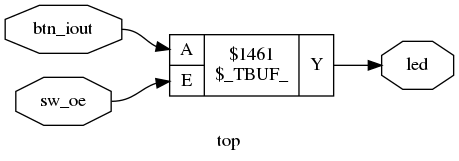

Test Case 1: OBUFT inference in place of $_TBUF_ in a top-level module:

-

sources:

module top ( input wire sw_oe, input wire btn_iout, output wire led ); assign led = sw_oe ? btn_iout : 1'bz; endmodule

- before `iopadmap`:

- after `iopadmap`:

- comment:

This case is correctly resolved

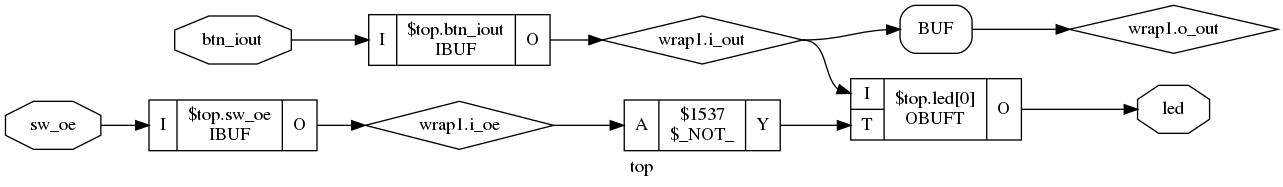

### Test Case 2: OBUFT inference in place of `$_TBUF_` in a submodule:

- sources:module top ( input wire sw_oe, input wire btn_iout, output wire led );

pad_wrapper wrap1 (sw_oe, btn_iout, led);endmodule

module pad_wrapper ( input wire i_oe, input wire i_out, output wire o_out );

assign o_out = i_oe ? i_out : 1'bz;endmodule

- before `iopadmap`:

- after `iopadmap`:

- comment:

This case is correctly resolved

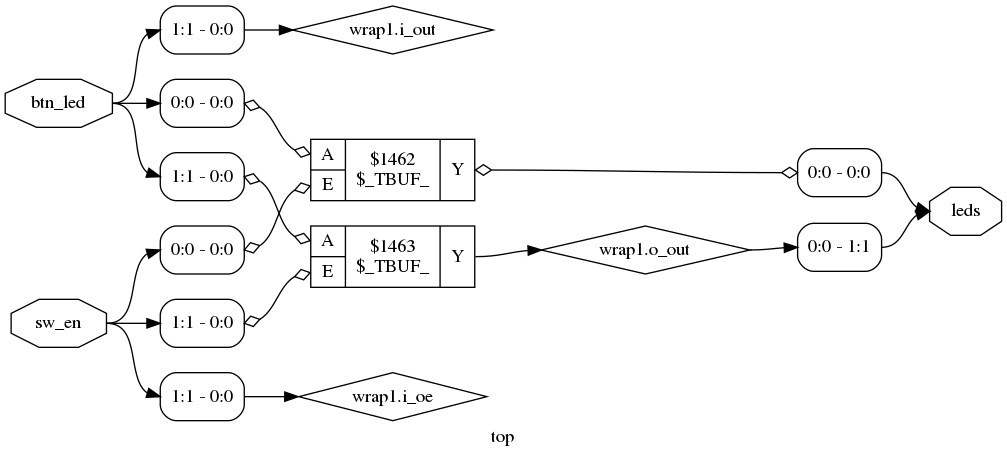

### Test Case 3: Mixed case

- sources:module top ( input wire [1:0] sw_en, input wire [1:0] btn_led, output wire [1:0] leds );

assign leds[0] = sw_en[0] ? btn_led[0] : 1'bz;

pad_wrapper wrap1 (sw_en[1], btn_led[1], leds[1]);endmodule

module pad_wrapper ( input wire i_oe, input wire i_out, output wire o_out );

assign o_out = i_oe ? i_out : 1'bz;endmodule

- before `iopadmap`:

- after `iopadmap`:

- comment:

It seems that the mixed case of the two previous scenarios causes problems. I noticed that the top-level module output is not directly connected to the `$_TBUF_` output in the last case.

Maybe this is a source of the problems.

Here are all the tests with synthesis scripts:

[yosys_obuft.zip](https://github.com/YosysHQ/yosys/files/5283918/yosys_obuft.zip)

@mwkmwkmwk Do you have any thoughts, how this issue might be resolved?

Steps to reproduce the issue

Testcase: obuft_inference_bug.zip

make top.edifto generate the invalid EDIF.Expected behavior

The final EDIF should contain OBUFT primitives instead of TBUF.

Actual behavior

When there is

assign IO_UTX = (cio_uart_tx_en_d2p ? cio_uart_tx_d2p : 1'bz);in the top module theOBUFTis correctly inferred. However if I have the statement inside a submodule I end up with_TBUF_cells which are obviously not recognized in Vivado.