Hi! I could make it work by introducing another time delay in the loop ` for i in range(0,len(daqdat)): print(i) timeStart = time.time()

time.sleep(n_pts/fs)

dev.write_Zynq_AXI_register_uint32(TRIG_REG, 0)

dev.write_Zynq_AXI_register_uint32(TRIG_REG, 1) # Start with trig need to stay high to register external trig

dev.write_Zynq_AXI_register_uint32(TRIG_REG, 0)

time.sleep(n_pts/fs)

status = 0

while status == 0:

status = dev.read_Zynq_AXI_register_uint32(STATUS_REG)

data_in = dev.read_Zynq_ddr(data_addr-START_ADDR, int(2*n_pts))

print('Elapsed time for receiving= {}'.format(time.time() - timeStart))

# data_in = np.fromstring(data_in, dtype=np.uint32) # Uncomment this line if you want to read data as 32 bits (useful if both ADCs are connected to counter)

data_in = np.fromstring(data_in, dtype=np.int16) # Uncomment this line if you want to read data as 16 bits

print('Elapsed time for conversion = {}'.format(time.time() - timeStart))

daqdat[i,:]=data_indd=np.transpose(daqdat) plt.plot(dd)

however, in this case, we arrive at a very slow acquisition speed. moreover, changing the decimation factor to 64 or 2048 makes it not working.

Hi Alex,

First of all, thank you a lot for releasing the new version, I have had my hands on it just now - it is very cool and easy to use (I use a non-GUI version). Decimation works perfectly (I know it is with no averaging). However, I noticed that the on-trigger acquisition behaves weird.

To explain the issue, here is how my signal looks like (trigger signal is in blue, I connected it to the 2nd channel just to record them synchronously): The signal period is 0.1 s.

These rectangular pulses (0..3.3V) I use for on-trigger acquisition for the 1st channel (orange signal is of my interest for stable acquisition).

The signal period is 0.1 s.

These rectangular pulses (0..3.3V) I use for on-trigger acquisition for the 1st channel (orange signal is of my interest for stable acquisition).

Further, the reference signal connected to the EXT_TRIG pin, I run your script (non-GUI),

for

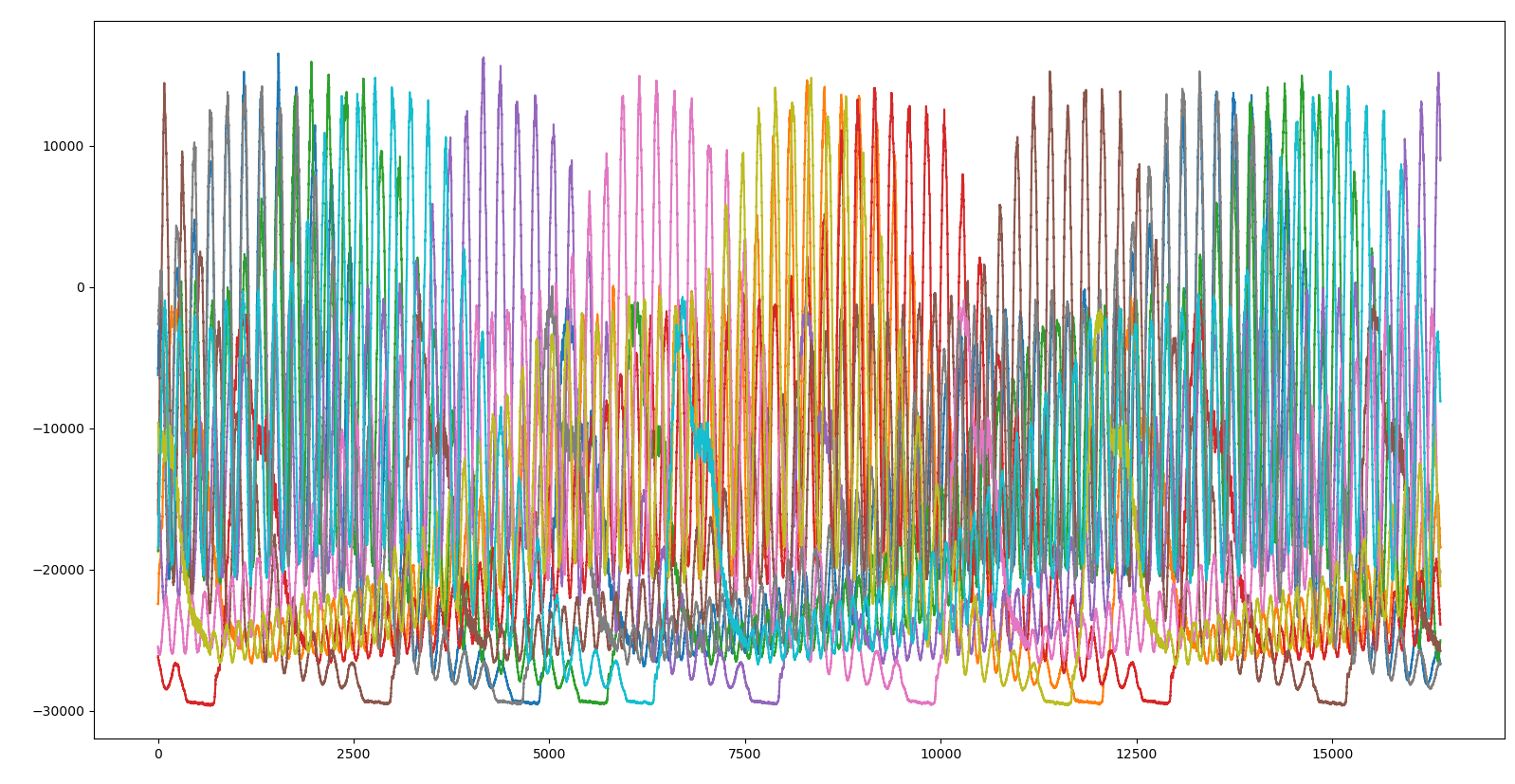

bUseTrig = 0I clearly see that on-trigger ACQ is OFF (as the recorded signals are randomly places in the time domain):when

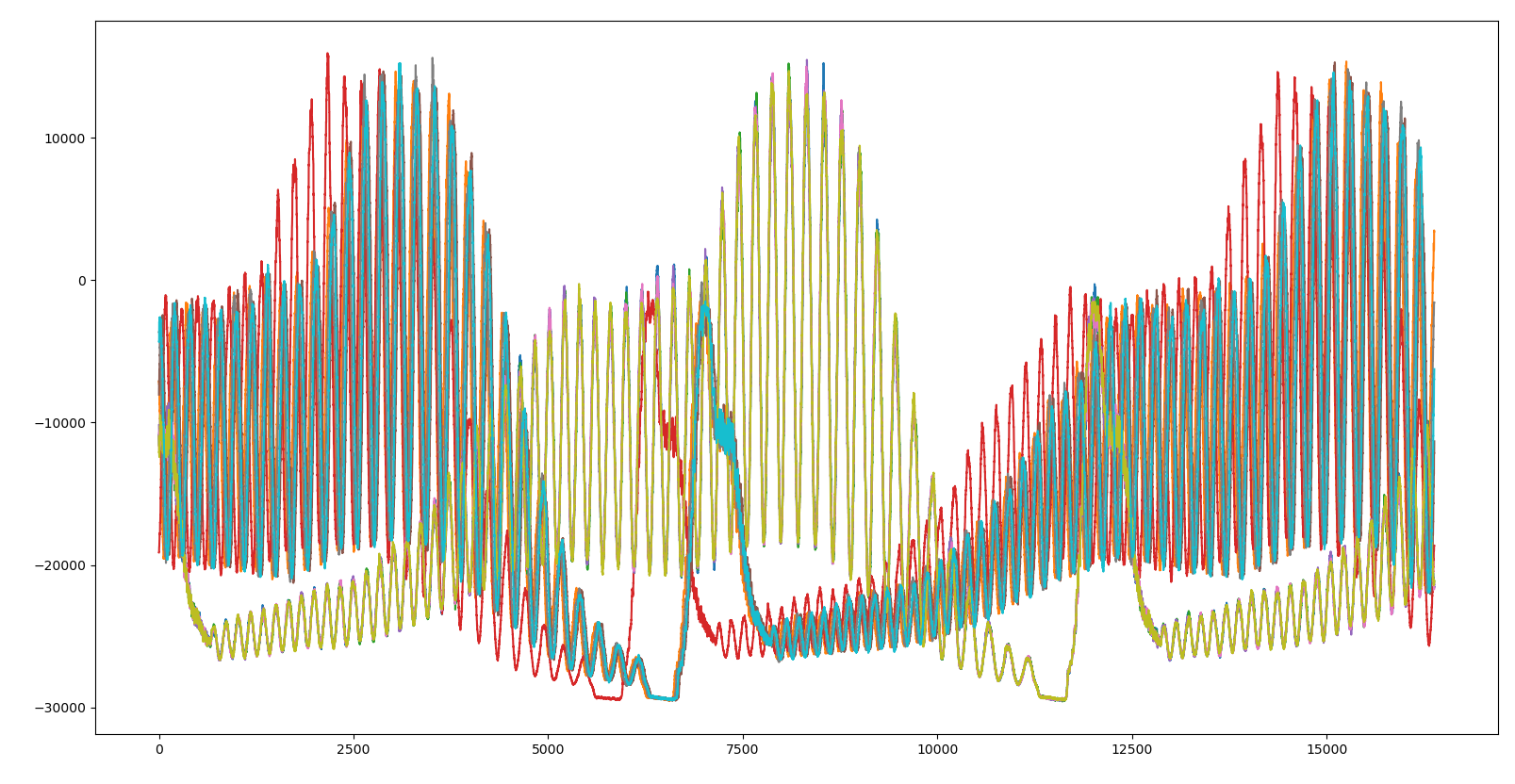

bUseTrig = 1on trigger ACQ is ON and it can be seen, but something like 50% of the signal is being shifted (and sometimes there are small shifts as well). Here I recorded 10 cycles withbUseTrig = 1, in this case, 5 cycles overlap well and 5 do overlap but with some shift relative to the first 5 (also they are quite unstable in phase actually).Do you have an idea from where this problem could come from? I have tried to play with some parameters but did not succeed. Also, I tried to feed ideal signals to the RP generated using a function generator, the results are the same. I also played with the phase for the signal, but it did change nothing.