The reason there are blocking assignments is to make it possible to use the result of the assigment in the same clock cycle as the assignment itself.

Example:

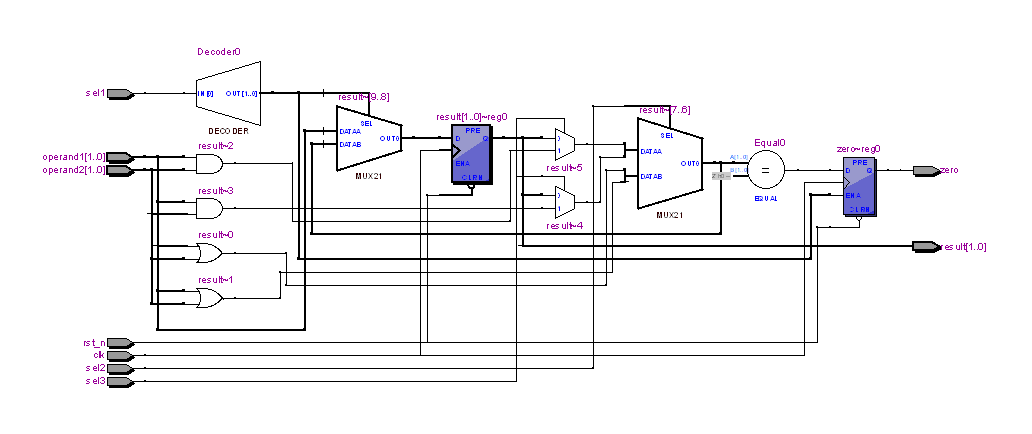

[...] // OR,OR to mem,OR to Dn if(decoder_alu_reg[0]) result[31:0] = operand1[31:0] | operand2[31:0]; // AND,AND to mem,AND to Dn else if(decoder_alu_reg[1]) result[31:0] = operand1[31:0] & operand2[31:0]; [...]

// Z sr[2] <= `Z; // <-- the Z macro uses the result[31:0] value assigned above and checks is the result zero

I believe a more appropriate way to express the same behavior would be to use a wire with a continuous assignment and use only non-blocking assignments to registers.

I am downloading Xilinx ISE WebPACK right now to check on the errors. I hope to comment on this issue later this week.

There is someone else also working on porting the ao68000 to Xilinx, so I believe that in the near future a Xilinx-compatible version of ao68000 will appear on GitHub.

Best regards, Aleksander Osman.

ao68000.v line 2841 shows result assigned with a non-blocking assignment.

a068000.v line 2852 shows result assigned with a blocking assignment.

I don't know what that the Altera synthesizer does with mixed assignment like this but Xilinx XST will fail and report an error.

This occurs in many places and I am sure that if this design ran on an Altera DE2-70 then the synthesizer resolved it in a consistent manner.

I could make them consistent in the source but I need to know what behavior is intended in the design.

thanks, Aaron Boxer