In general, you should not generate clocks using logic; such clocks aren't guaranteed to work either in simulation (due to simulation semantics not being defined for such clocks) or in synthesis (due to LUTs not being glitchless on most FPGAs). See also #625.

When I was implementing a slave Quad SPI controller with amaranth I found two cases, one where the simulation indicates that the device will work, but in reality it does not, and another where in simulation it indicates that device will not work, but in reality it works. I have simplified the project and created a simplified serial controller with a FSM that is able to reproduce the issue. (Example can be found in the attachment along with examples of the two issues)

Issue 1: The simulation indicates that the device will work, but in reality it does not. This is the scenario in the attached example SimpleFSMClient1. In this case the simulation clock is set to be:

that is, the serial clock signal is only generated during the data transmission, when the CSn (negated Chip Select) signal is active. In this case, in reality, the FSM misses one extra clock cycle to come out of the FSM

Datastate into theIdlestate, thus failing to make it ready for receiving a second transfer. However in simulation despite the needed and missing extra clock cycle the simulation says it will come toIdlestate at the end of transfer, whenserialCSnsignal goes high/inactive. This simulation result is generated when the signals between the modules are set like so:The result can be seen here:

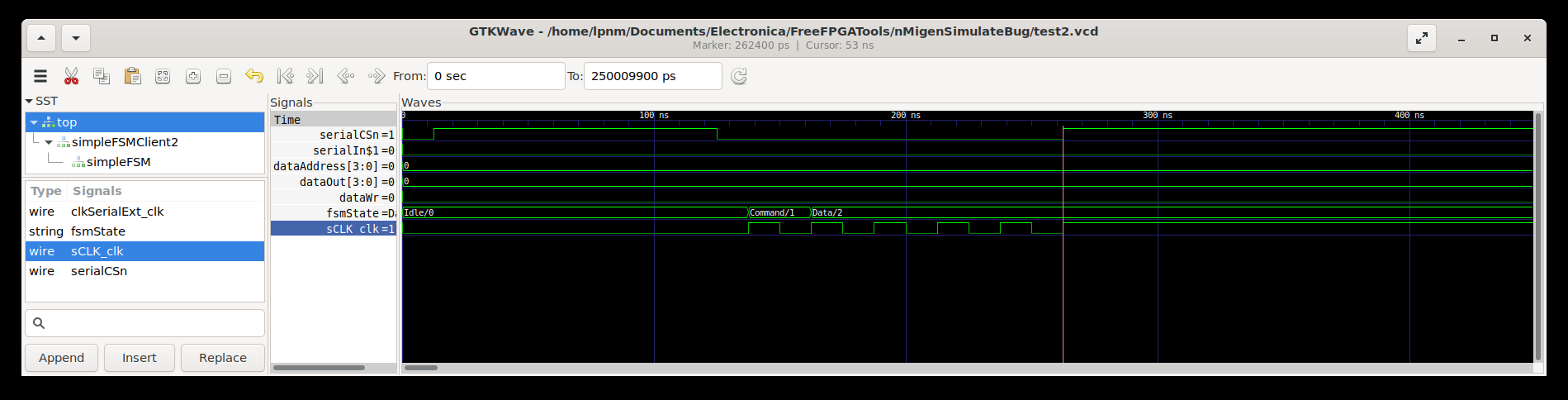

Issue 2: The simulation indicates that the device will not work, but in reality it does work. This is the scenario in the attached example SimpleFSMClient2. In this case the simulation clock is set to be:

that is, the serial clock is generated only when

serialCSnwhen signal is low/active and an extra clock cycle is generated by theserialCSnsignal itself. Here thesimpleFSMClient2.simpleFSM.fsmState != 0condition is not required in reality, but only for simulation, because serialCSn starts low by default, despite the simulation process setting it high as early as it can. The condition ensures that the extra cycle is only generated when the FSM machine has its current state set to a nonIdlestate.This scenario was tested with a Xilinx XC7S15 (Spartan-7) and is working properly in the device. The simulation however indicates that the FSM machine will get stuck in the

Datastate, thus failing the second transfer. This simulation result is caused when the followingserialCSnsignal assignment is used:as depicted here:

In summary:

serialCSnis assigned with:serialCSnis assigned with:Datastate at the end of the first transferIdlestate at the end of the first transferSimpleFSM.txt SimpleFSMClient1.txt SimpleFSMClient2.txt