Hi @HuyKhac , Sorry for late reply. I've tested with your code on the latest master with following log print:

ESP_LOG_BUFFER_HEX(TAG, reg_data, 4);

for (int i = 0; i< 4; i++) {

printf("%d, %d\n", reg_data[i]&0x40, reg_data[i]&0x4);

}When I connect GPIO 22 to VCC, it shows:

I (286) test: cc cc cc cc

64, 4

64, 4

64, 4

64, 4While below if connect GPIO 22 to GND:

I (286) test: 88 88 88 88

0, 0

0, 0

0, 0

0, 0This means in some way the QIO mode can reads from DAT2 correctly. The reason is possibly:

- Your IDF version is too old, please try again on the latest master.

- Your LA don't get the data correctly. Please set the threshold to 1.6v or so and try again.

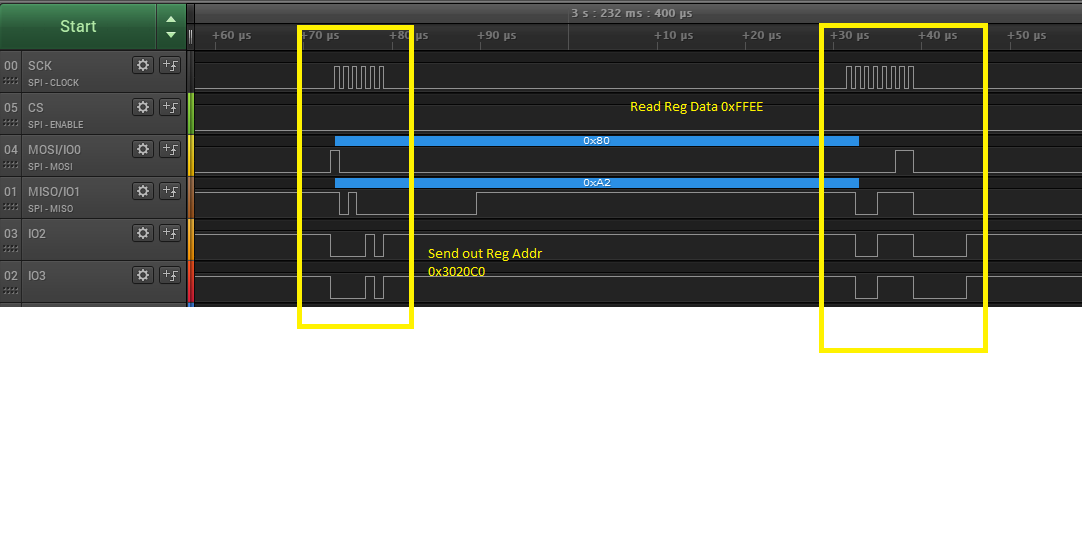

- Seen from the LA waveform you attached, data comes out at the negedge on the first 8 clocks (mode 0); However, data comes out at posedge (mode 1) on the 10th clock, but negedge at edge on the later clocks (mode 0). It seems that the slave return data only 2 clocks by mode 1 and DATA are then controlled by sth else (maybe the master or floating) at later clocks. I guess, only first four clocks are returned by the slave, so the return value should be 0xEE 0x00 (seen from mode1). Please check the slave's data sheet to see the communication format, and check which mode to use.

I've no your commit ID, neither your slave spec. And your return data length (BBAA, 16 bits) doesn't match your total length on the snapshot (4x8bits). So I cannot tell whether it's which reason. Please try the ways above, and if you still have problem, please comback with more information (slave spec, actual reg_data value (4bytes), commit id).

Zoom-in to show data signal lines

Zoom-in to show data signal lines

Zoom-in to show data signal lines

Zoom-in to show data signal lines

Environment

Problem Description

I try to use VSPI in QSPI mode to increase communication speed. ESP32 can write out register address, but when it reads back register data, IO2 bit is always read as 0 although it is 1 in a probed waveform. Here is my code to configure VSPI in QSPI mode:

The register addr is 0x3020C0 and the expected register data is 0xFFEE. However, ESP32 reads back as 0xBBAA ( all IO2 bits are read as 0). If IO2 bits are read as 1 then, it will return 0xFFEE which is expected. I capture the waveform to check, IO2 bits are correctly output by slave device, but ESP32 always read as 0s.

I attach the waveform here. Note that in reading reg data phase, it reads 4 bytes but uses last 2 bytes (that requirement comes from the slave device.

Here is the print log from ESP32 showing that it reads back reg data as 0xBBAA

Should I miss anything? Is there any bugs in SPI driver in QSPI mode?

This is the waveform I captured for that the test. It shows correct waveform sent from the slave device

Thanks, Huy