Hello,

Please send here your sdkconfig file and your code to setup master in order to reproduce the issue. Also please enable the DEBUG log verbosity in your master project then start communication. Attach the log here.

If the master sends the request with even parity, then slave configured with odd parity should not receive the request from master and will not respond. The debug log can give you more information about parity check on master side. I can expect some issues with your configuration of odd parity on master side but even parity should work just fine.

D (25397) MB_MASTER_SERIAL: Timeout occured, processed: 9 bytes

D (25407) MB_PORT_COMMON: xMBMasterPortSerialGetResponse default

D (25407) MB_PORT_COMMON: eMBMasterRTUReceive: Port enter critical.

D (25417) MB_PORT_COMMON: eMBMasterRTUReceive: Port exit critical

E (25427) MB_PORT_COMMON: Drop incorrect frame, receive_func(4) != send_func(1)

D (25437) MB_PORT_COMMON: eMBMasterPoll:EV_MASTER_ERROR_PROCESS

D (25437) MB_PORT_COMMON: vMBMasterErrorCBReceiveData:Callback receive data timeout failure.

D (25447) Err rcv buf: 01 00 08 00 08

D (25447) MB_PORT_COMMON: eMBMasterWaitRequestFinish: returned event = 0x100

D (25457) MB_CONTROLLER_MASTER: mbc_serial_master_get_parameter: Bad response to get cid(8) = ESP_ERR_INVALID_RESPONSE

E (25467) MB_CONTROLLER_MASTER: mbc_master_get_parameter(73): Master get parameter failure, error=(0x108) (ESP_ERR_INVALID_RESPONSE).

E (25477) MASTER_TEST: Characteristic #8 (RelayP2) read fail, err = 0x108 (ESP_ERR_INVALID_RESPONSE).

D (25797) MB_PORT_COMMON: xMBPortSerialWaitEvent, UART event: 5

D (25797) MB_MASTER_SERIAL: MB_uart[2] event:

D (25797) MB_MASTER_SERIAL: uart parity error. <<<<<<<<<<<<<<<<<<<< Parity errors detected and frame is not excepted

D (25807) MB_PORT_COMMON: xMBPortSerialWaitEvent, UART event: 5

D (25807) MB_MASTER_SERIAL: MB_uart[2] event:

D (25817) MB_MASTER_SERIAL: uart parity error.

D (25817) MB_PORT_COMMON: xMBPortSerialWaitEvent, UART event: 5

D (25827) MB_MASTER_SERIAL: MB_uart[2] event:

D (25827) MB_MASTER_SERIAL: uart parity error.

D (25837) MB_PORT_COMMON: xMBPortSerialWaitEvent, UART event: 5

D (25837) MB_MASTER_SERIAL: MB_uart[2] event:

D (25847) MB_MASTER_SERIAL: uart parity error.

D (25847) MB_PORT_COMMON: xMBPortSerialWaitEvent, UART event: 5

D (25857) MB_MASTER_SERIAL: MB_uart[2] event:

D (25857) MB_MASTER_SERIAL: uart parity error.

D (25867) MB_PORT_COMMON: xMBPortSerialWaitEvent, UART event: 5

D (25867) MB_MASTER_SERIAL: MB_uart[2] event:

D (25877) MB_MASTER_SERIAL: uart parity error.

D (25877) MB_PORT_COMMON: xMBPortSerialWaitEvent, UART event: 5

D (25887) MB_MASTER_SERIAL: MB_uart[2] event:

D (25887) MB_MASTER_SERIAL: uart parity error.

D (25897) MB_PORT_COMMON: xMBPortSerialWaitEvent, UART event: 5

D (25897) MB_MASTER_SERIAL: MB_uart[2] event:

D (25907) MB_MASTER_SERIAL: uart parity error.

D (25907) MB_PORT_COMMON: xMBPortSerialWaitEvent, UART event: 0

D (25917) MB_MASTER_SERIAL: MB_uart[2] event:

D (25917) MB_MASTER_SERIAL: Data event, len: 8.

D (25987) MB_PORT_COMMON: xMBMasterRunResTake:Take resource (80) (41 ticks).

D (25987) MB_PORT_COMMON: eMBMasterPoll:EV_MASTER_FRAME_TRANSMIT

D (25987) POLL transmit buffer: 04 00 00 00 02

D (25987) MB_PORT_COMMON: eMBMasterRTUSend: Port enter critical.

D (25997) MB_PORT_COMMON: eMBMasterRTUSend: Port exit critical

D (25997) MB_PORT_COMMON: xMBMasterPortSerialSendRequest default

D (26007) MB_PORT_COMMON: vMBMasterPortTimersRespondTimeoutEnable Respond enable timeout.Thank you.

Our device acting as a Modbus master does not appear to check parity values on receive frames from the slave device. In our test setup, the ESP master is configured for even parity and connected to a slave test device which transmits back with odd parity. However, the master does not recognize the parity error and calls to mbc_master_send_request() return without error. This also occurs when the master and slave are configured for even and odd parity, respectively.

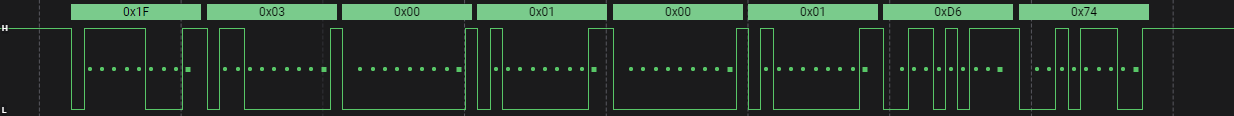

Here is a capture of the master sending a valid request frame with even parity:

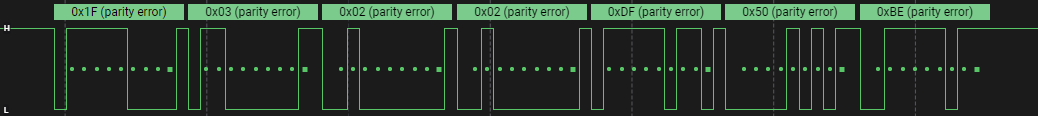

And here is the slave's invalid response which is still accepted:

The only condition in which errors are returned is when an unexpected number of bits is received (i.e. master is configured for no parity bits but slave returns even/odd parity, or the slave returns an additional stop bit).