Hmmm, fuses are to prevent fire. Typically located at the source so you remove the source of energy. I typically don't size fuse to protect the devices, I typically size to protect the wires or things that can catch fire. I also don't like fuses, it's hard to properly size them for I2T issues. In this case the pulsing will cause high amps for short periods of time, so I2T issues are elevated. I tend to think the fuse should be closer to the panel, if it should be there at all. Some times I use a fuse as it's easier to repair then a burnt copper trace.

L1 includes Digikey part number 495-5076-ND. The schematic properties includes part numbers for either JLC or Digikey. I was planning for 12AWG wire, and I used this prediction tool to predict 6 wraps. https://coil32.net/online-calculators/ferrite-torroid-calculator.html I think 10AWG might also fit, but insulation thickness is likely a concern. Of course if you need more windings, then it may not work either.

I recently found the below. Any thoughts about cramming 50A through a SO8 package? https://jlcpcb.com/partdetail/MagnTek-MT9223CT50BR5/C2930869

I'm concerned about I2R on the traces. I included J33 and J34 as an option to add a copper wire to help keep the current off the PCB layers.

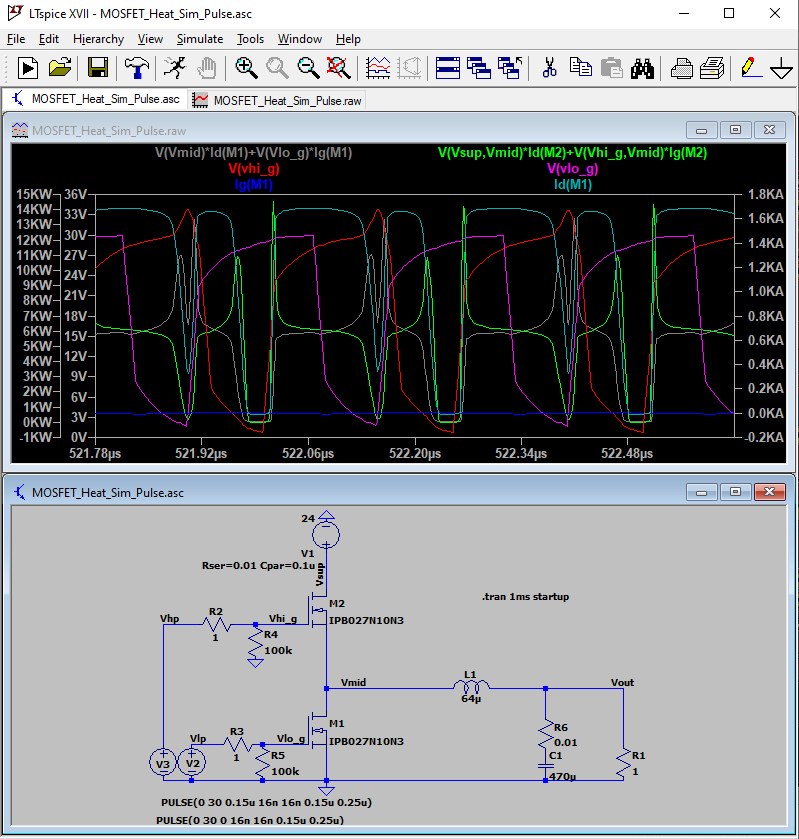

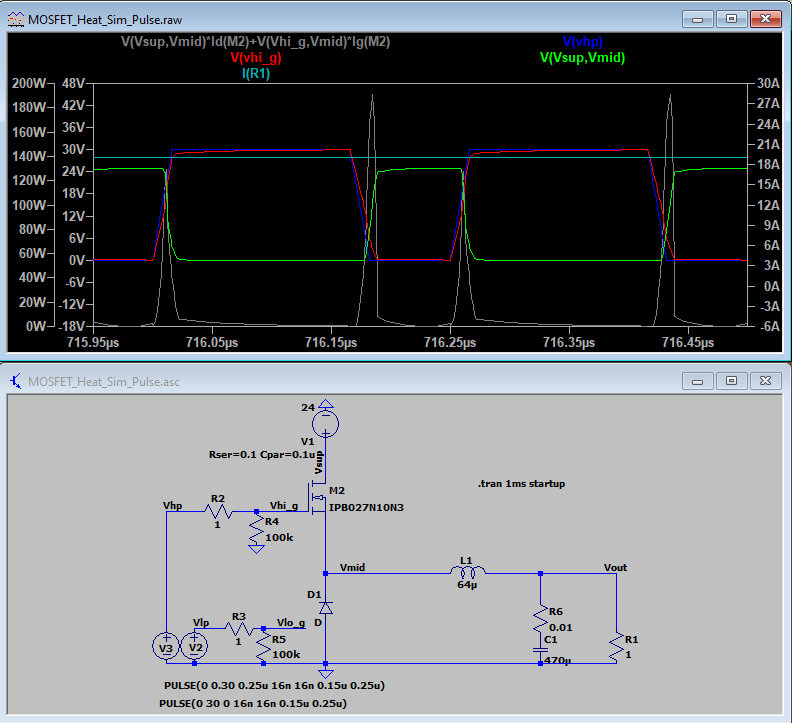

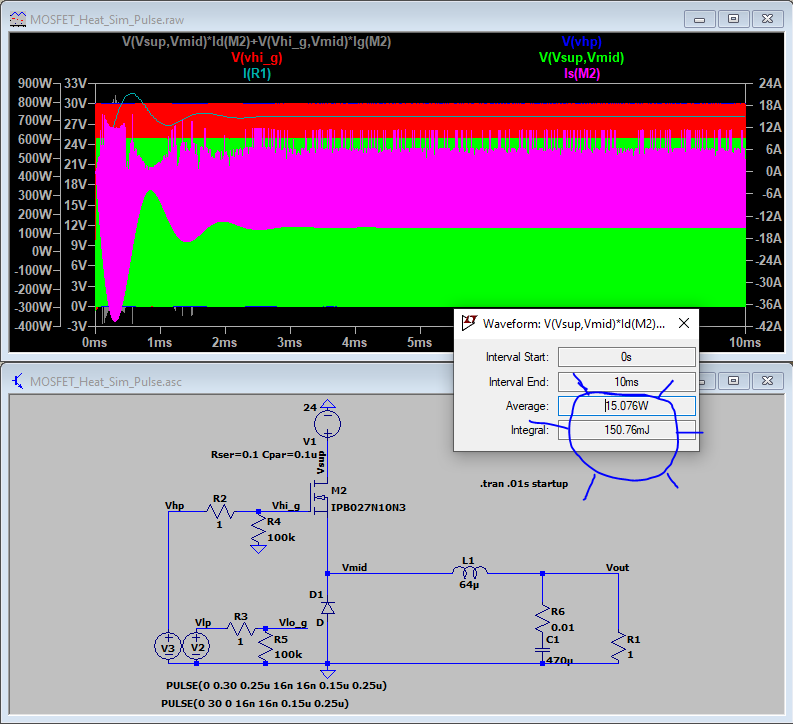

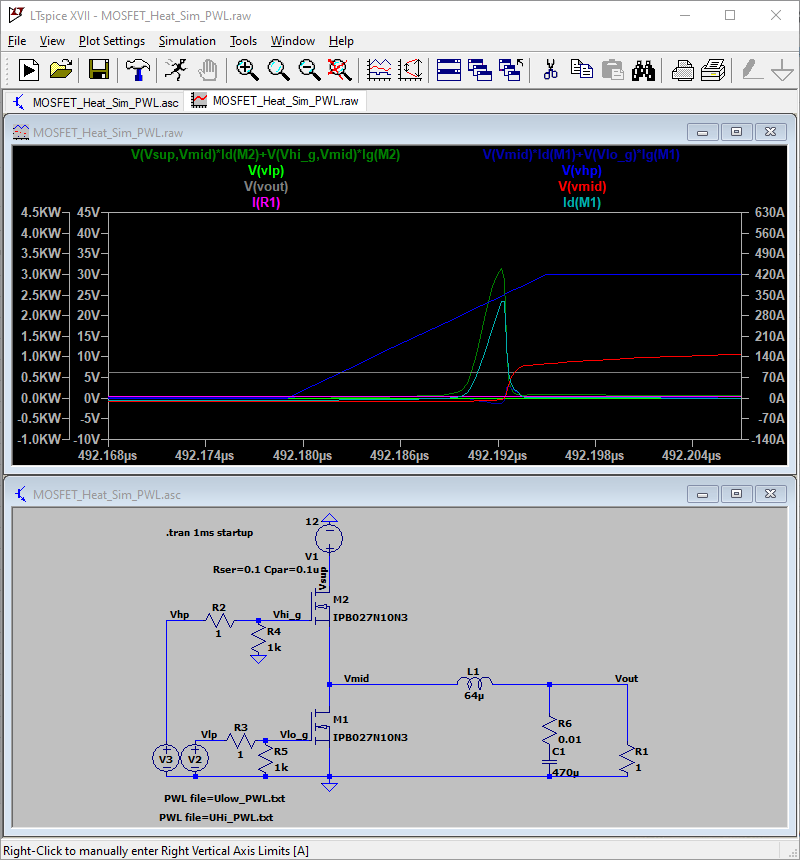

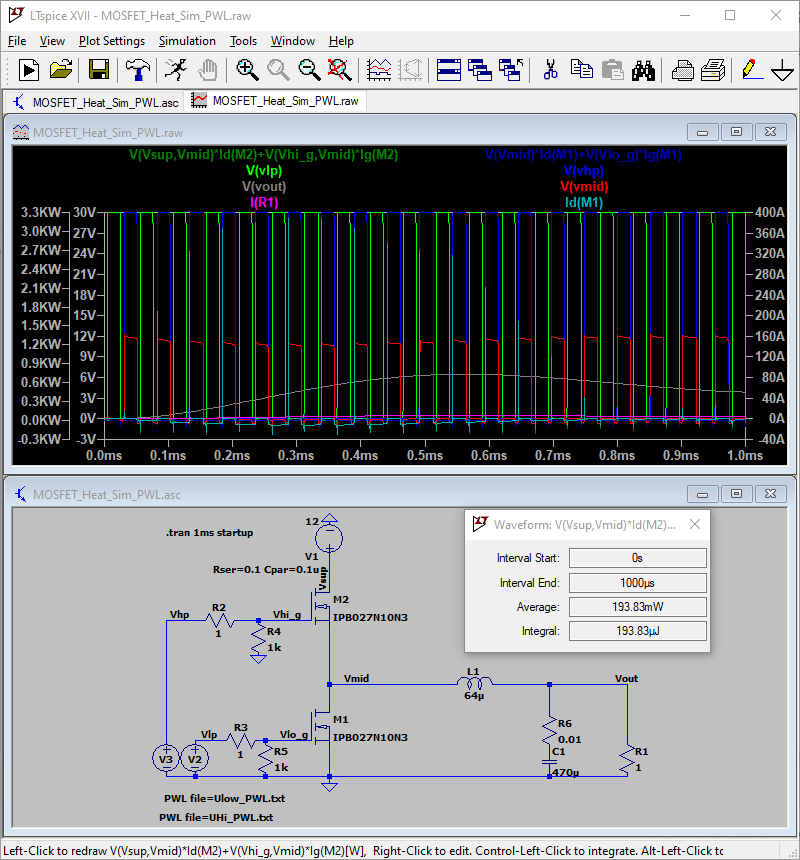

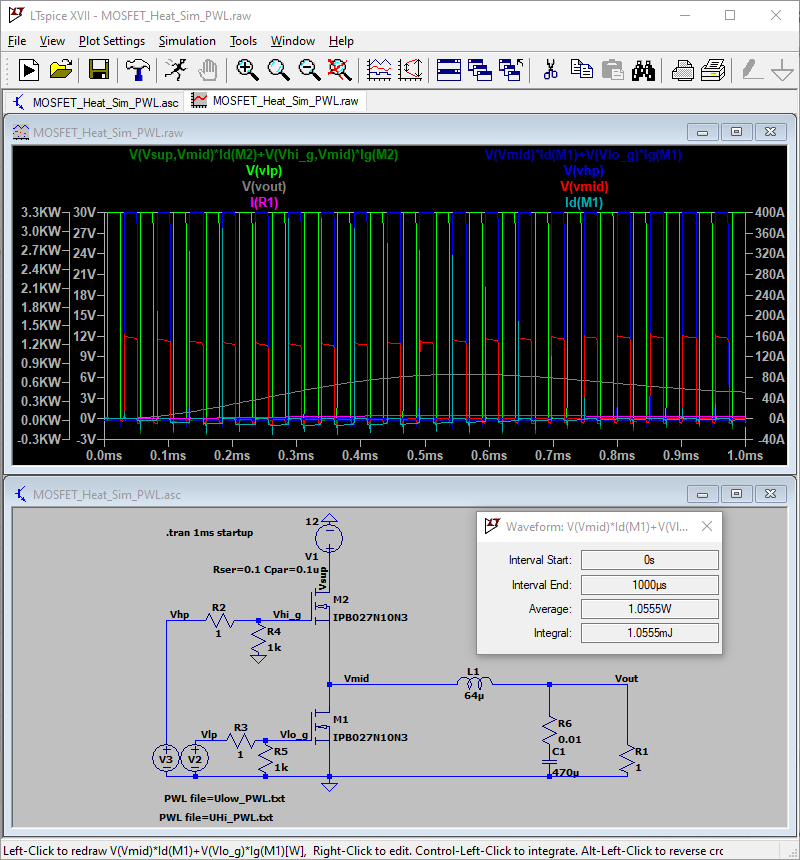

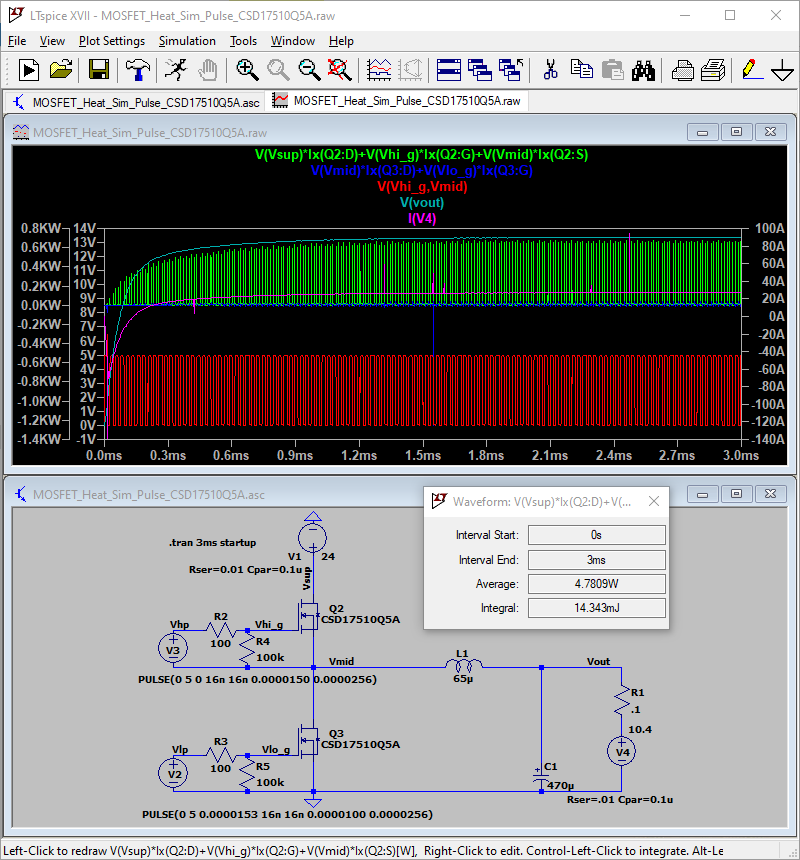

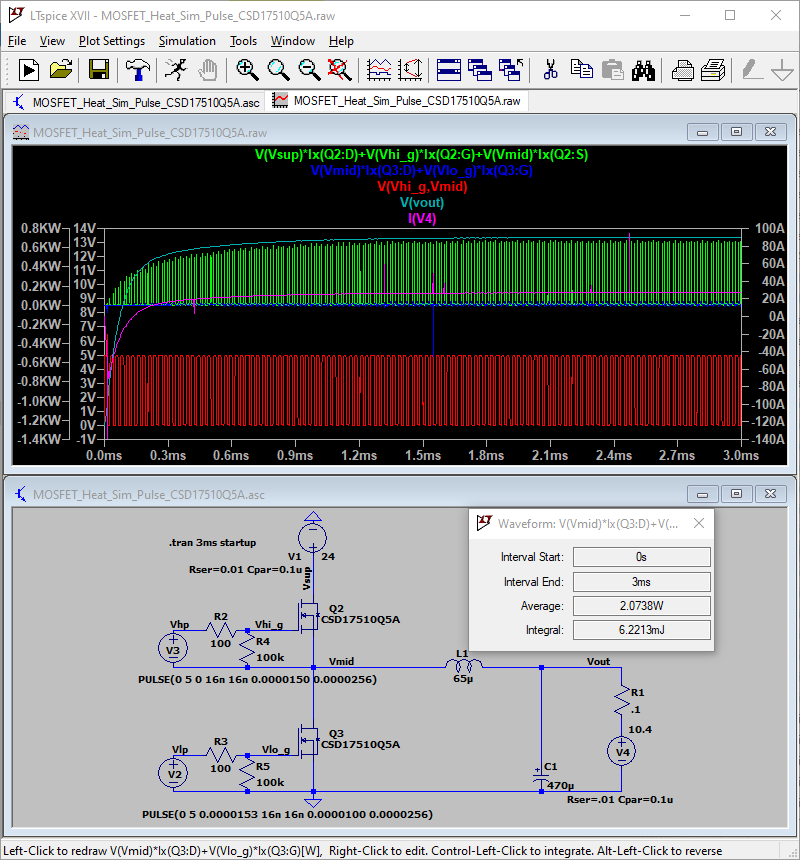

I was not able to make meaningful predictions of heat generated by Q1, Q2 or Q3. Rds generated watts was not helpful, the real heat will be the transient conditions. 2.6mOhm * 35A^2 = 3W. I don't much about what the losses will be during the switching. How many watts do we think we need to get out of these? Q3 also wants more electrical insulation from the heatsink. Which isn't going to help the situation. I also should pick a fan and some how include that in the 3D printed case. If I had some kind of prediction of the watts, or some kind of empirical data to work from, then I could make a better thermal prediction.

Q1 and Q2 secretly conduct a bunch of the electrical energy via the screw on the tab. I expect the copper layers are not large enough, but copper with tabs bolted together should be good. Looks like the C7 change will either be a huge layout change or I might just bolt the cap to heat sink. That's going to be a bit of work to change.

I hear you about the current loops. I'm expecting this to be around 20kHz. Is that a proper frequency to be expecting? I really don't know the low core frequency to be considering.

I'm USA eastern standard time. If a phone call helps perhaps we can phone.

(excuse the misaligned holes, I only had a hand drill on hand, when I assembled it)

In the worst case you will mount it to a bigger heatsink.

(excuse the misaligned holes, I only had a hand drill on hand, when I assembled it)

In the worst case you will mount it to a bigger heatsink.

Hi, I am no electronics guru, but here are my suggestions.

Schematic:

Layout: