第一章: 第二章: 第三章:

Open mchwang233 opened 1 month ago

第一章: 第二章: 第三章:

Double Data Rate Synchronous Dynamic Random Access Memory”(双数据率同步动态随机存储器)的简称 SDRAM的发展如下:

DDR SDRAM内存条从外观上可以看出由很多内存颗粒组成。从内存控制器到内存颗粒内部逻辑,笼统上讲从大到小为:Channel>DIMM>Rank>Chip>Bank>Row/Column,如下图:

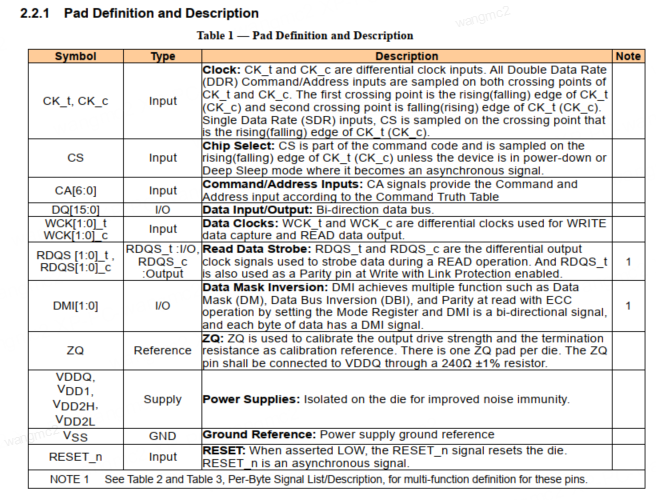

如DDR4芯片有20根地址线(17根Address、2根BA、1根BG),16根数据线。在搞清楚这些信号线的作用以及地址信号为何还有复用功能之前,我们先抛出1个问题。假如我们用20根地址线,16根数据线,设计一款DDR,我们能设计出的DDR寻址容量有多大?

Size(max)=(2^20) 16=1048576 16=16777216bit=2097152B=2048KB=2MB。

但是事实上,该DDR最大容量可以做到1GB,比传统的单线编码寻址容量大了整整512倍,它是如何做到的呢?答案很简单,分时复用。我们把DDR存储空间可以设计成如下样式:

首先将存储空间分成两个大块,分别为BANK GROUP0和BANK GROUP1,再用1根地址线(还剩19根),命名为BG,进行编码。若BG拉高选择BANK GROUP0,拉低选择BANK GROUP1。(当然你也可以划分成4个大块,用2根线进行编码)

在这里插入图片描述

此时,我们将DDR内存颗粒划分成了2个BANK GROUP,每个BANK GROUP又分成了4个BANK,共8个BANK区域,分配了3根地址线,分别命名为BG0,BA0,BA1。然后我们还剩余17根信号线,每个BANK又该怎么设计呢?这时候,就要用到分时复用的设计理念了。

剩下的17根线,第一次用来表示行地址,第二次用来表示列地址。现在修改为传输2次地址,在传输1次数据,寻址范围最多被扩展为2GB。虽然数据传输速度降低了一半,但是存储空间被扩展了很多倍。这就是改善空间。

所以,剩下的17根地址线,留1根用来表示传输地址是否为行地址。

所以1个BANK可以分成65536行,每行1024列,每个存储单元16bit。

所以1个BANK可以分成65536行,每行1024列,每个存储单元16bit。

每行可以存储1024*16bit=2048B=2KB。每行的存储的容量,称为Page Size。

单个BANK共65536行,所以每个BANK存储容量为65536*2KB=128MB。

单个BANK GROUP共4个BANK,每个BANK GROUP存储容量为512MB。

单个DDR4芯片有2个BANK GROUP,故单个DDR4芯片的存储容量为1024MB=1GB。至此,20根地址线和16根数据线全部分配完成,我们用正向设计的思维方式,为大家讲解了DDR4的存储原理以及接口定义和寻址方式。

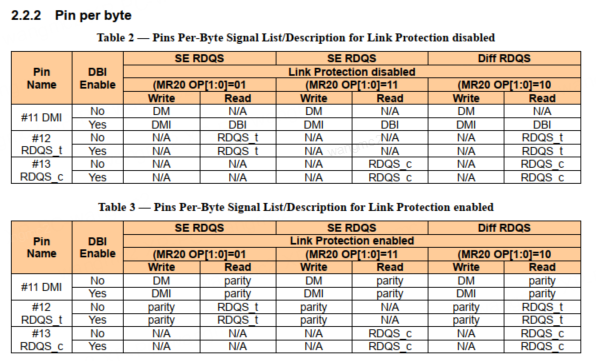

一版是SE、DIFF、SEC

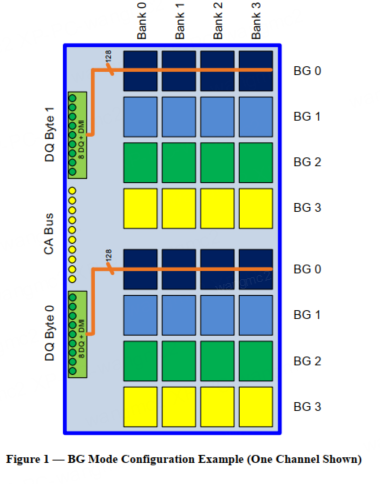

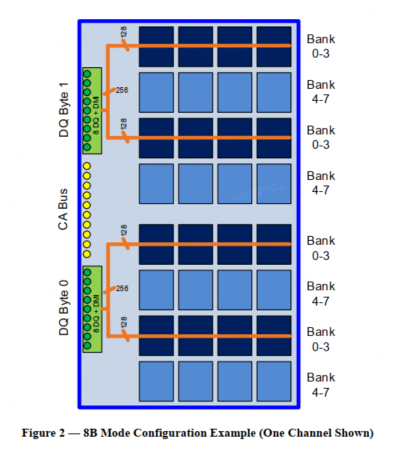

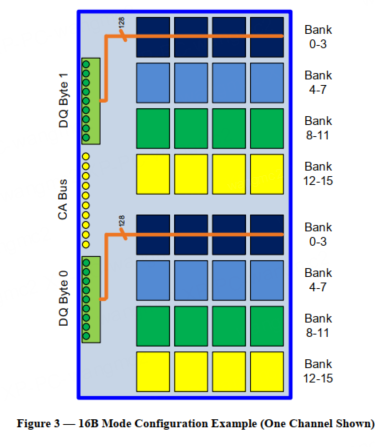

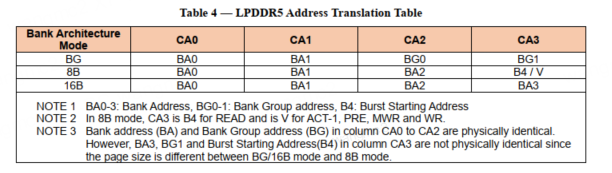

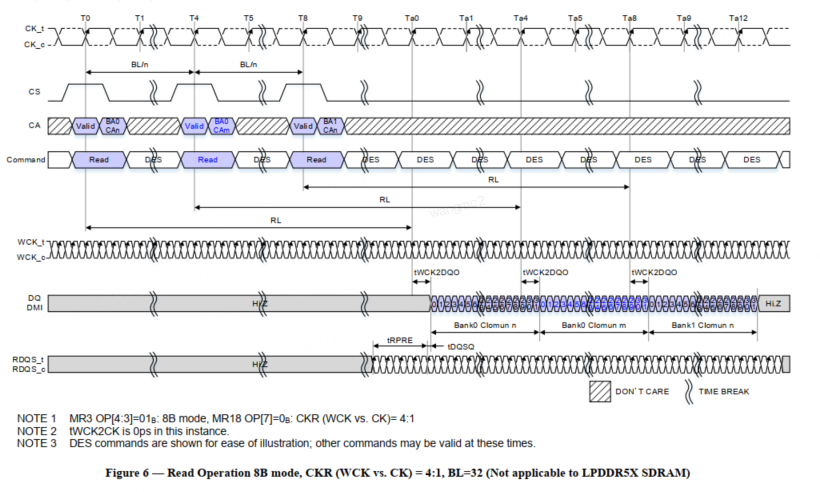

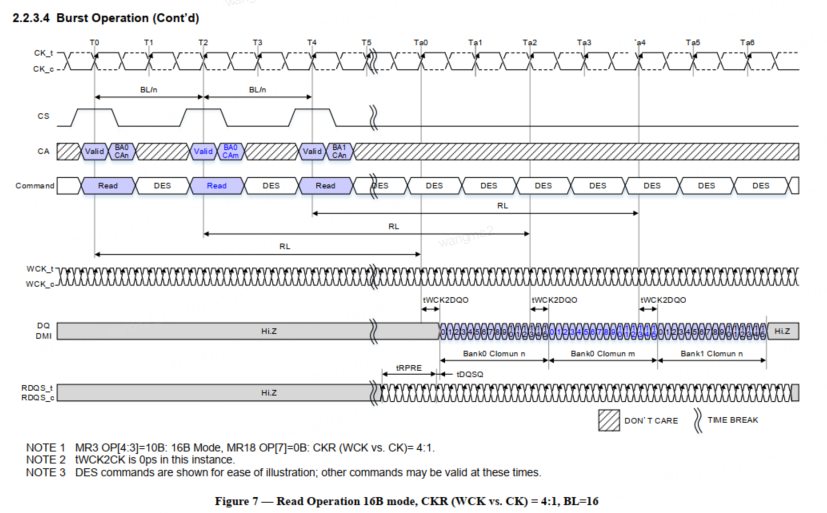

这里主要是LPDDR5 主要支持三种模式 BG mode 、8B mode、16B mode

这些mode很核心的是要和CA结合去看:

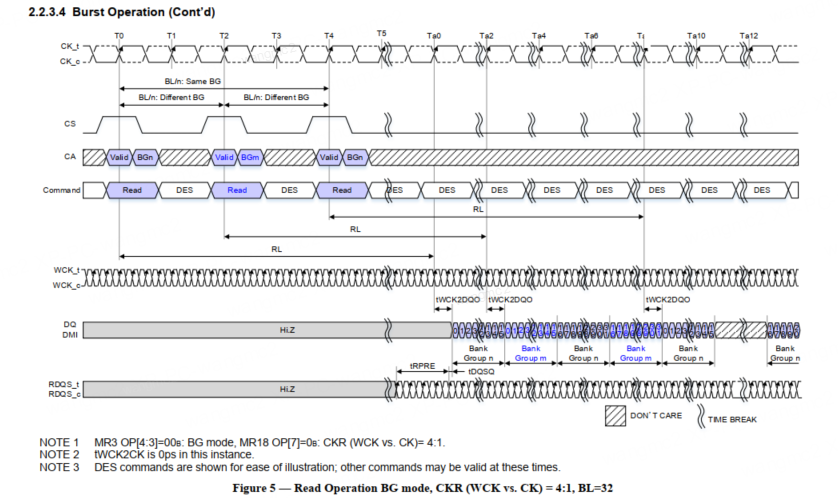

BG mode

在交织的情况下,BG mode是支持BL32的传输的

The BG Mode architecture only supports BL32 in an interleaved fashion when the WCK and CK ratio is 4:1. BL32 interleaved Reads will output the first word of DQ[15:0] after a certain latency from the Read command. The second word, consisting of DQ[31:16], will begin to be driven after an 8tWCK gap from the end of the first word. Figure 5 depicts BG mode Read operations for BL32 including the interleaving between bank groups. If correctly implemented, Read(BL16) command and Read32(BL32) commands can be mixed; however once a Read32(BL32) command is issued, issuing Read(BL16)/Read32(BL32) command after 3 clocks is prohibited, to avoid read data conflict. 8B mode

16B mode

https://zhuanlan.zhihu.com/p/663697786 https://www.systemverilog.io/design/ddr4-initialization-and-calibration/ https://www.systemverilog.io/design/lpddr5-tutorial-physical-structure/ https://www.systemverilog.io/design/understanding-ddr4-timing-parameters/ https://www.systemverilog.io/design/ddr4-basics/

https://wmchappy.cn/2018/08/03/lpddr/