Bleep bloop!

LabVIEW Diff Robot here with some diffs served up hot for your pull request.

Notice something funny? Help fix me on my GitHub repo.

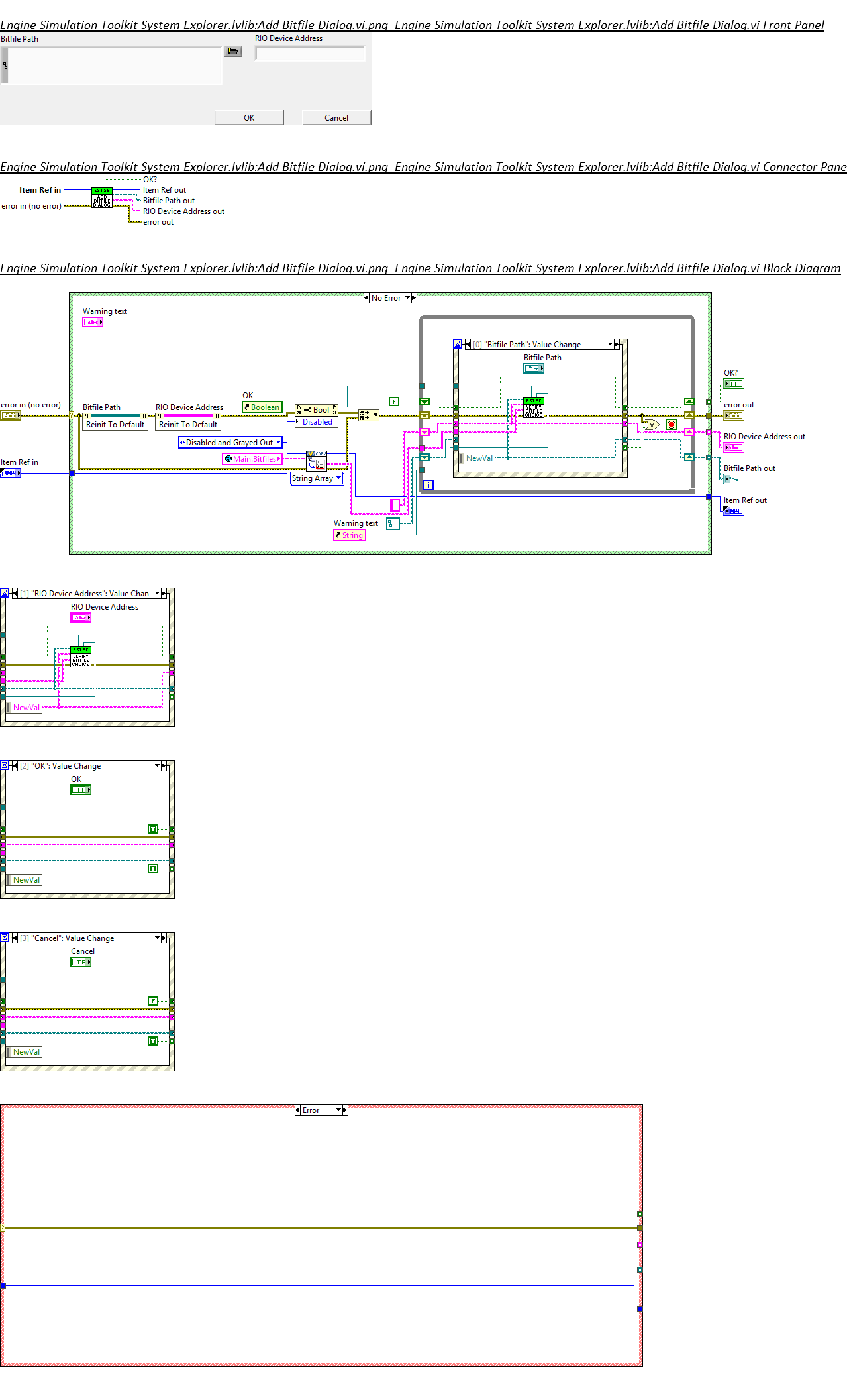

Engine Simulation Toolkit System Explorer.lvlib--Add Bitfile Dialog.vi.png:

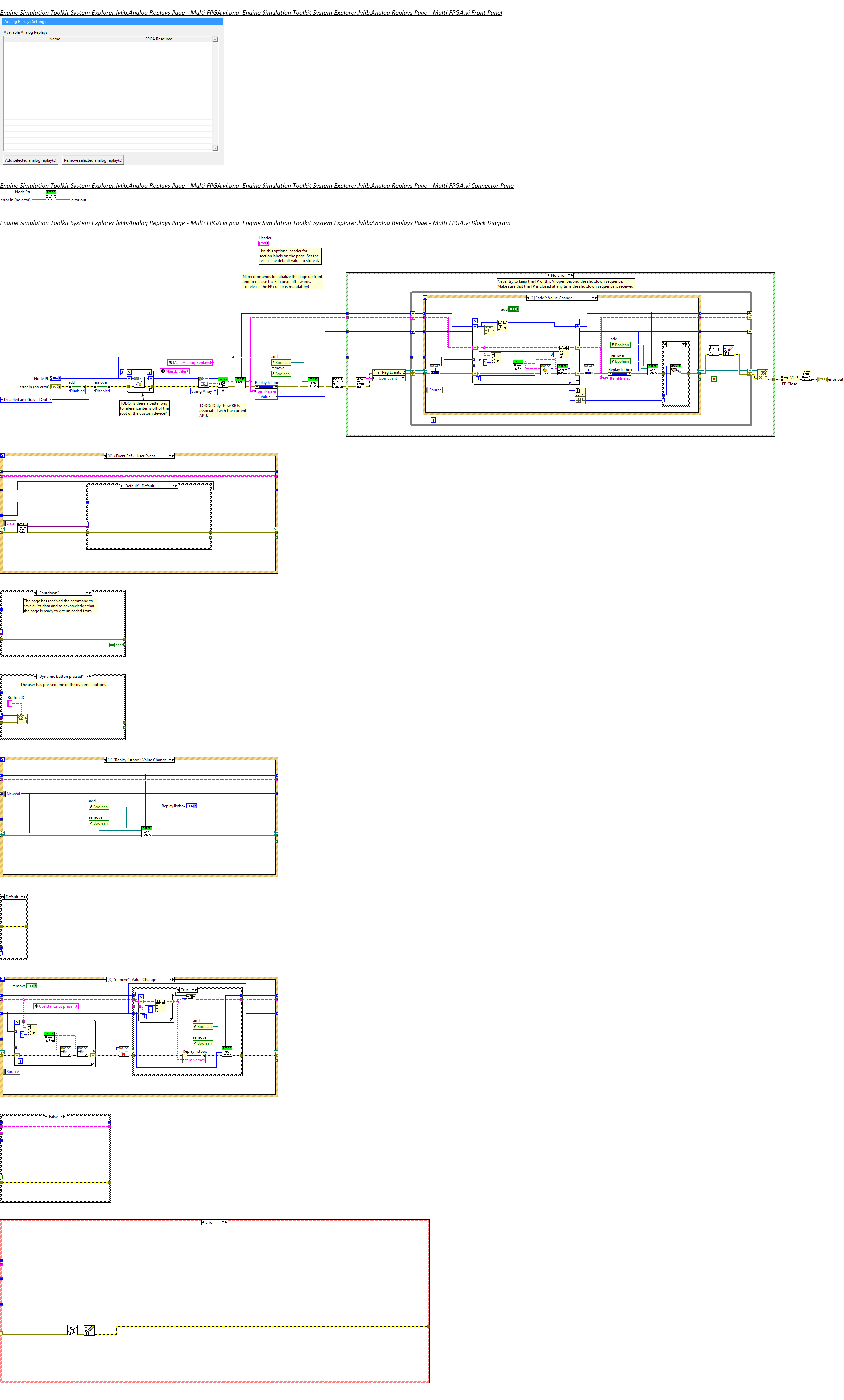

Engine Simulation Toolkit System Explorer.lvlib--Analog Replays Page - Multi FPGA.vi.png:

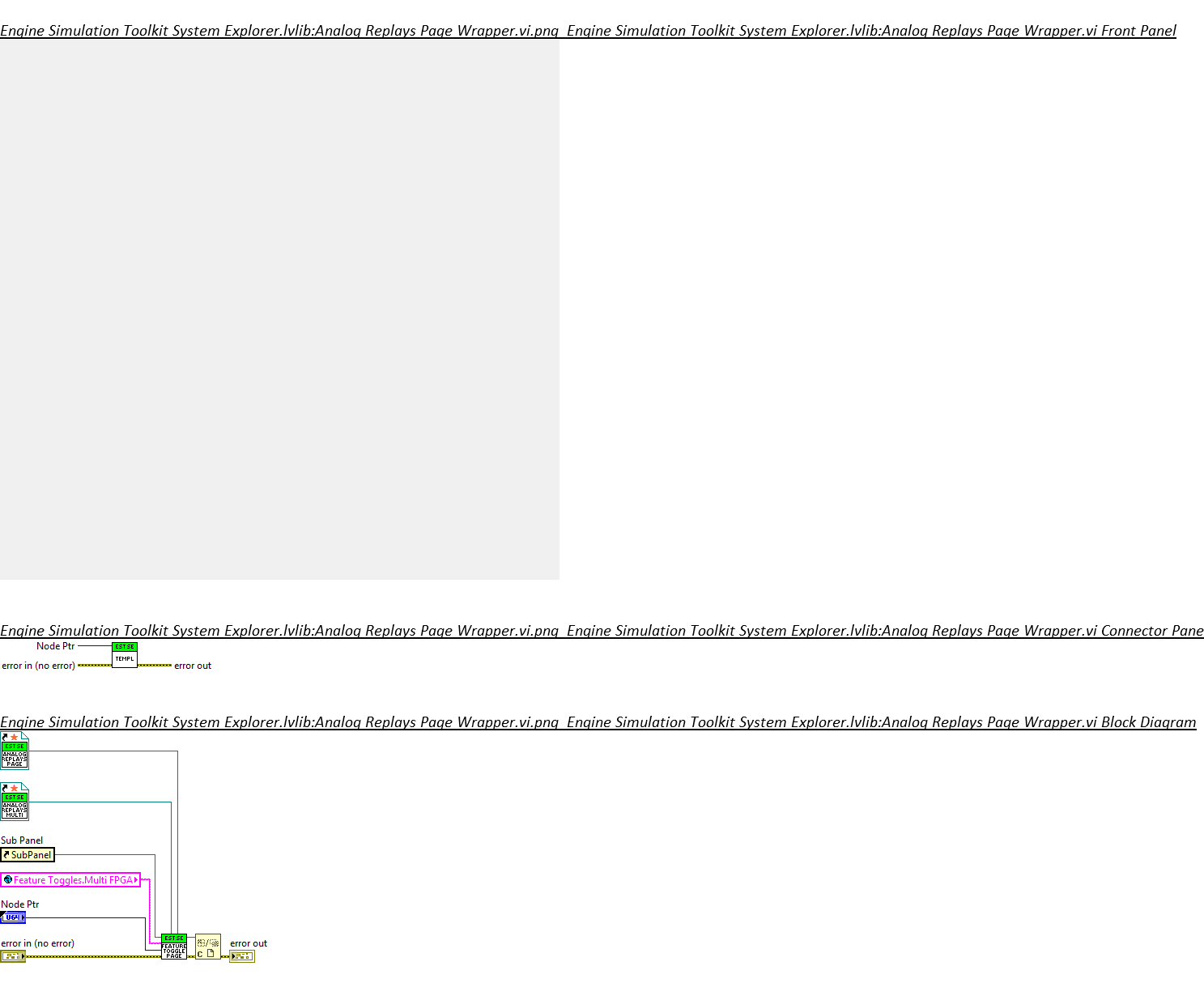

Engine Simulation Toolkit System Explorer.lvlib--Analog Replays Page Wrapper.vi.png:

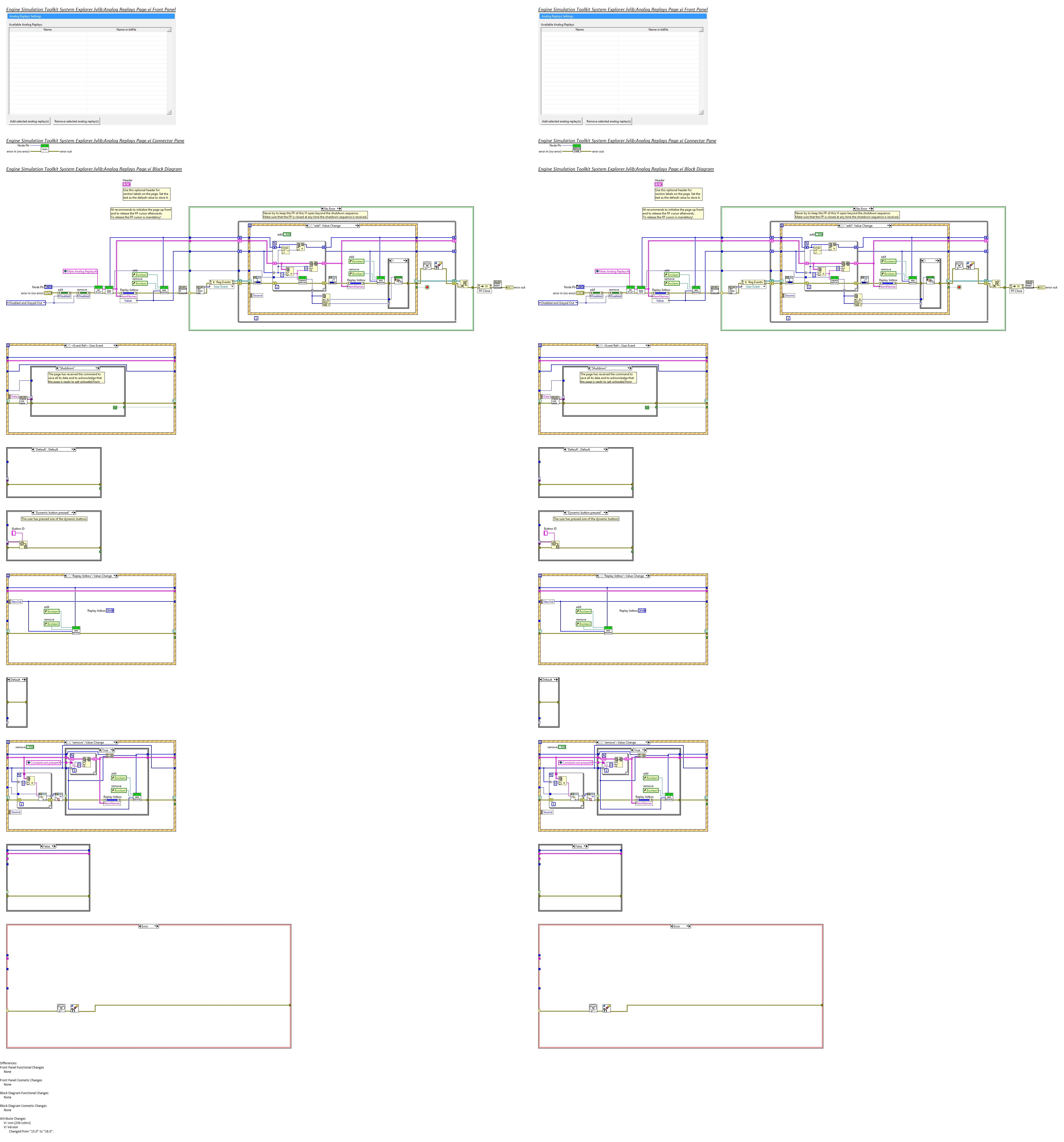

Engine Simulation Toolkit System Explorer.lvlib--Analog Replays Page.vi.png:

Engine Simulation Toolkit System Explorer.lvlib--APU Page - Multi FPGA.vi.png:

Engine Simulation Toolkit System Explorer.lvlib--APU Page Wrapper.vi.png:

Engine Simulation Toolkit System Explorer.lvlib--APU Page.vi.png:

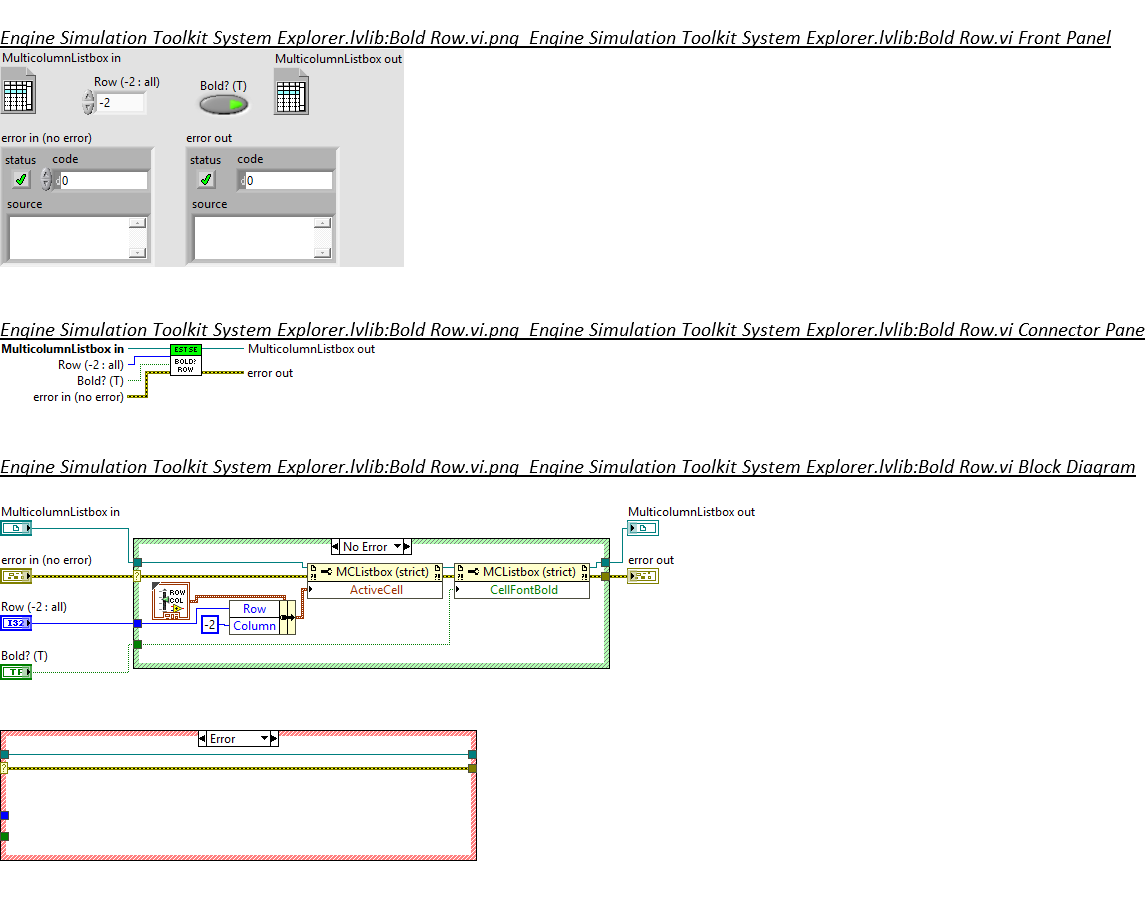

Engine Simulation Toolkit System Explorer.lvlib--Bold Row.vi.png:

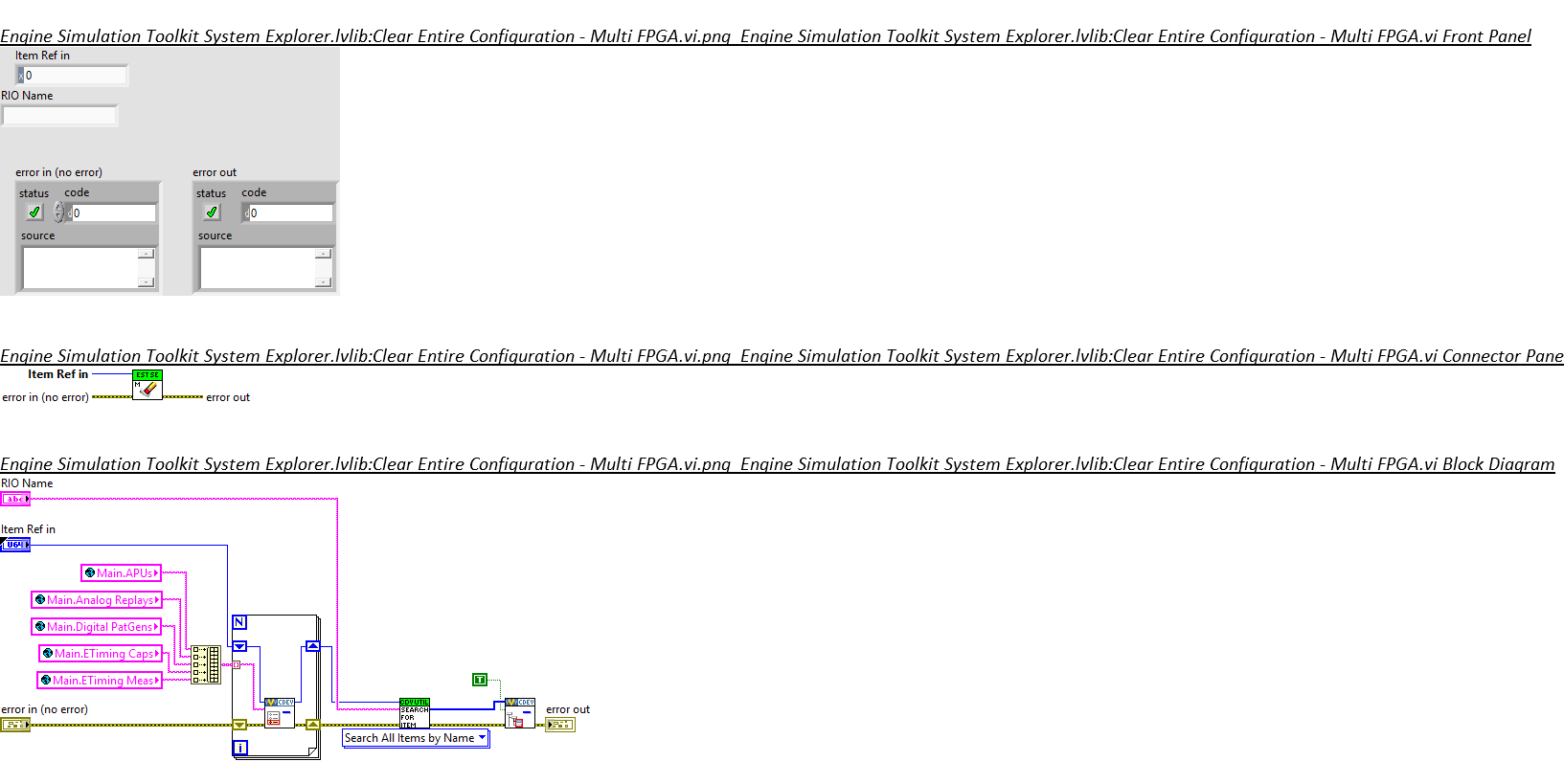

Engine Simulation Toolkit System Explorer.lvlib--Clear Entire Configuration - Multi FPGA.vi.png:

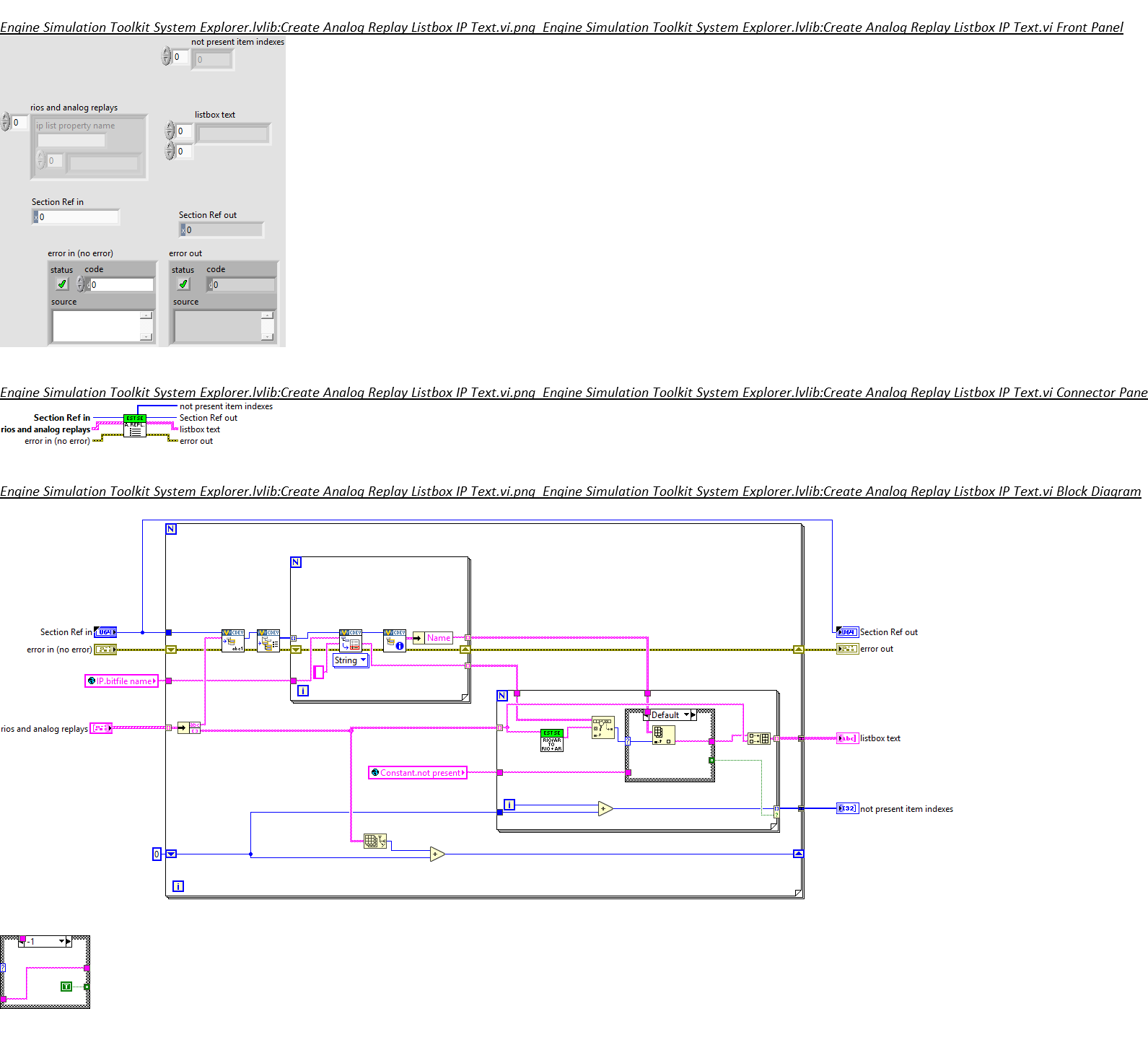

Engine Simulation Toolkit System Explorer.lvlib--Create Analog Replay Listbox IP Text.vi.png:

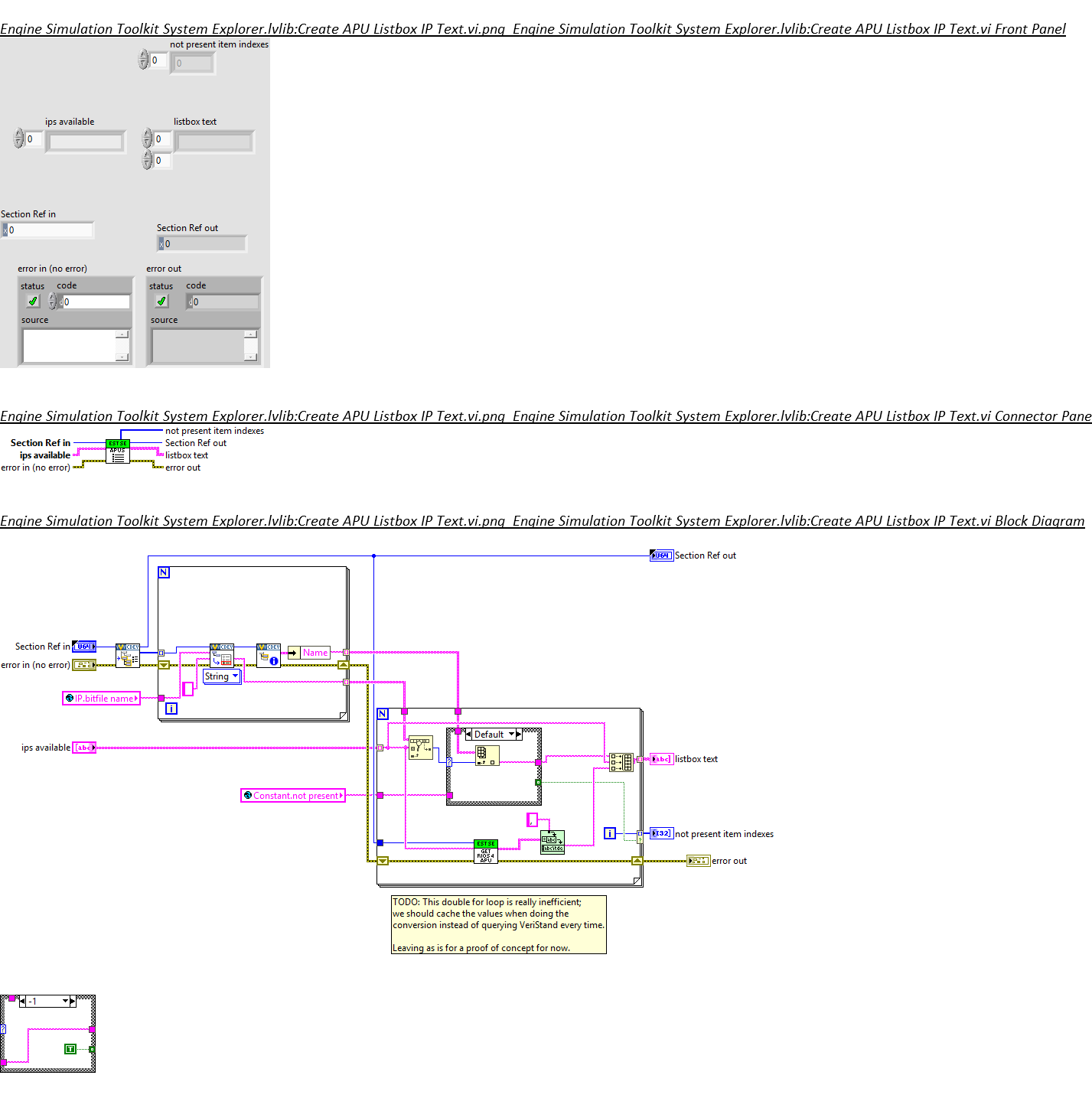

Engine Simulation Toolkit System Explorer.lvlib--Create APU Listbox IP Text.vi.png:

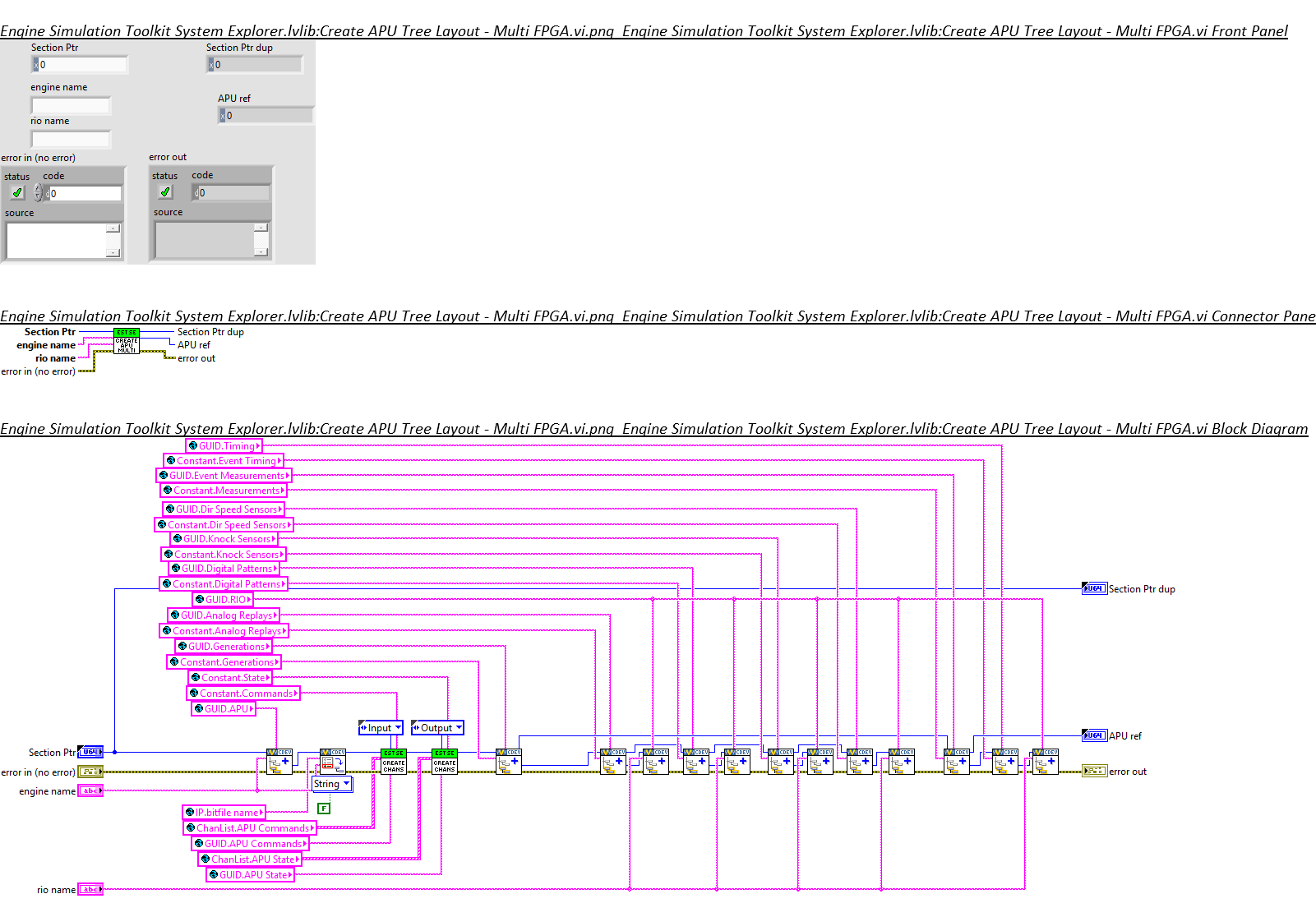

Engine Simulation Toolkit System Explorer.lvlib--Create APU Tree Layout - Multi FPGA.vi.png:

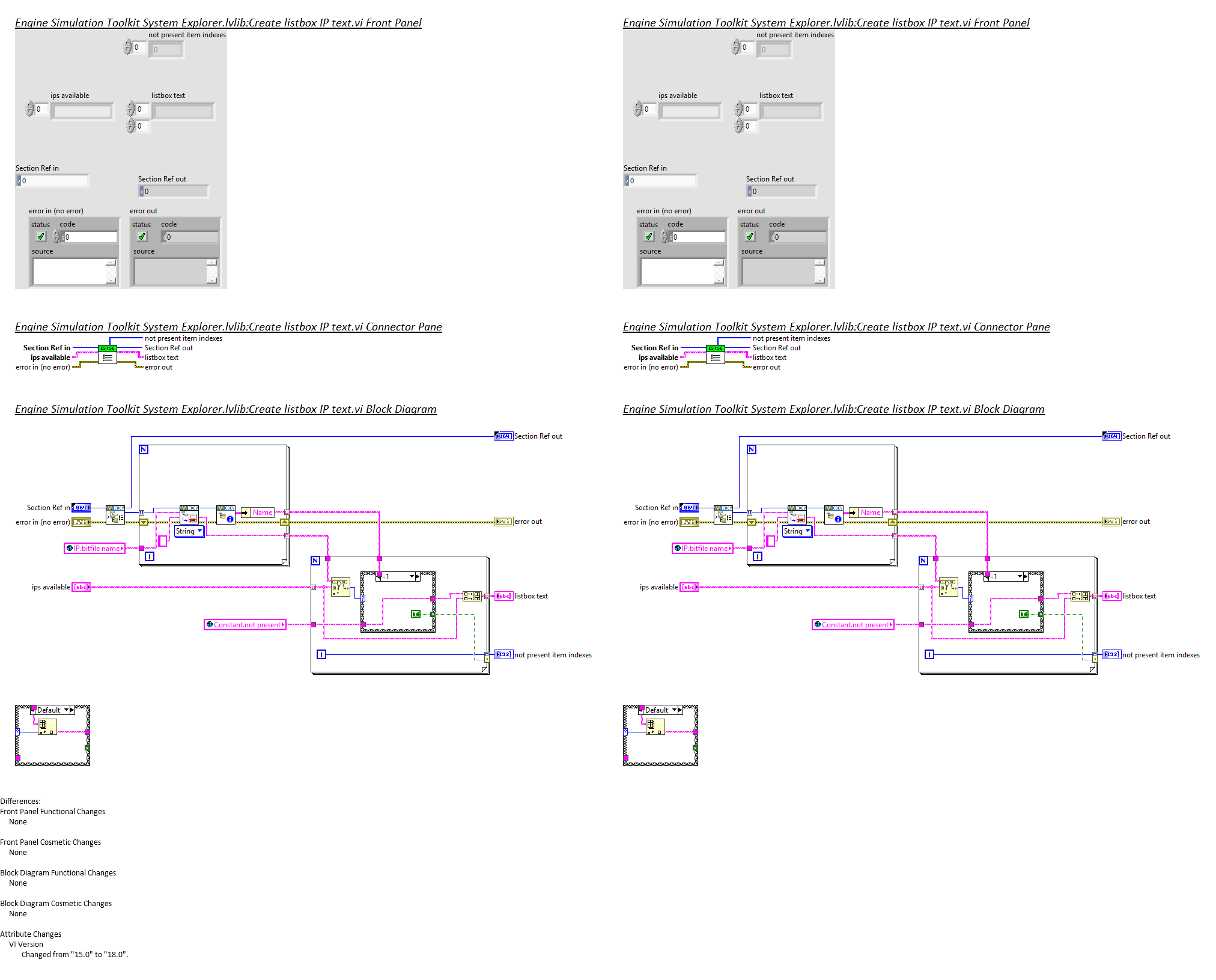

Engine Simulation Toolkit System Explorer.lvlib--Create listbox IP text.vi.png:

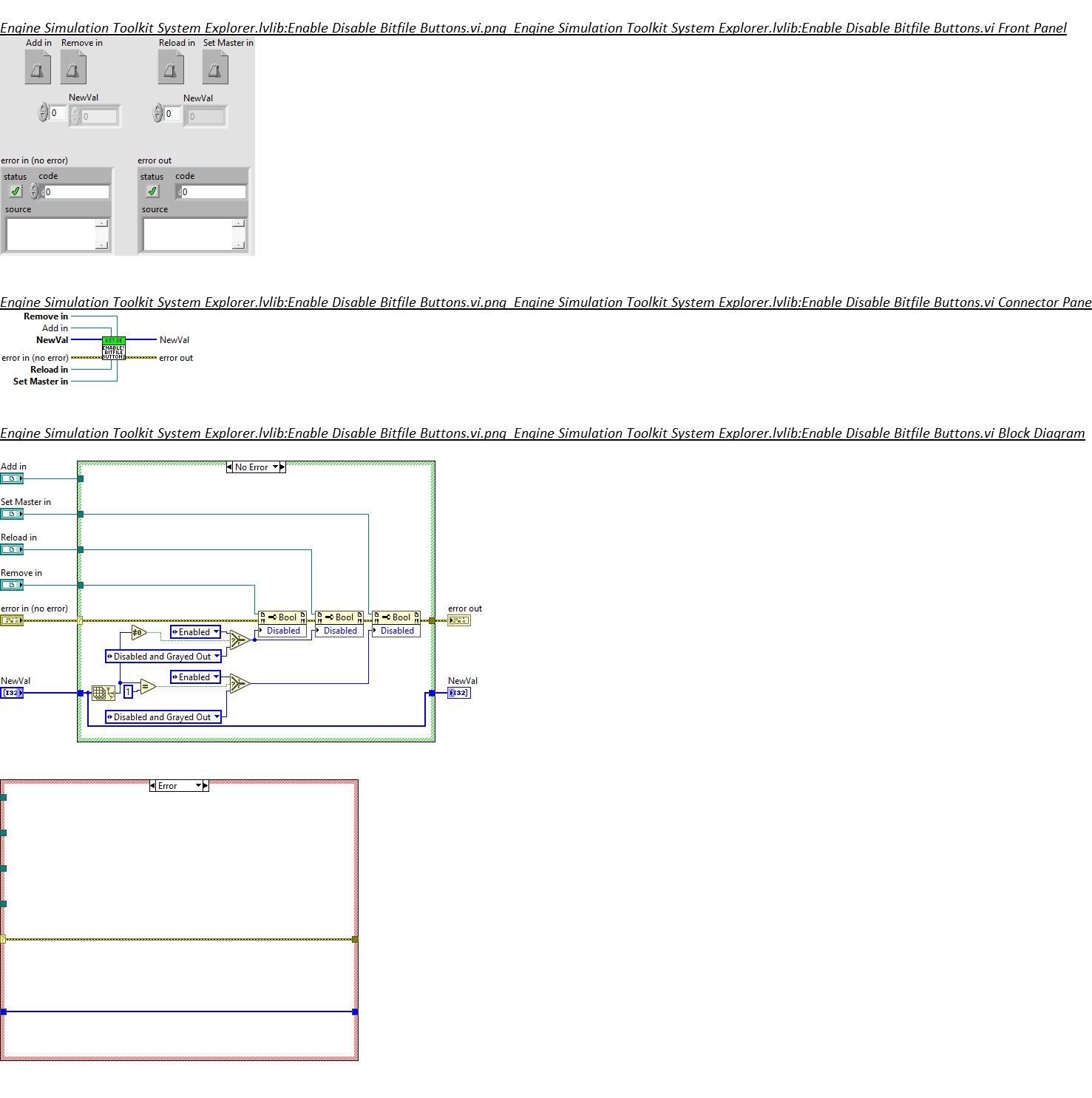

Engine Simulation Toolkit System Explorer.lvlib--Enable Disable Bitfile Buttons.vi.png:

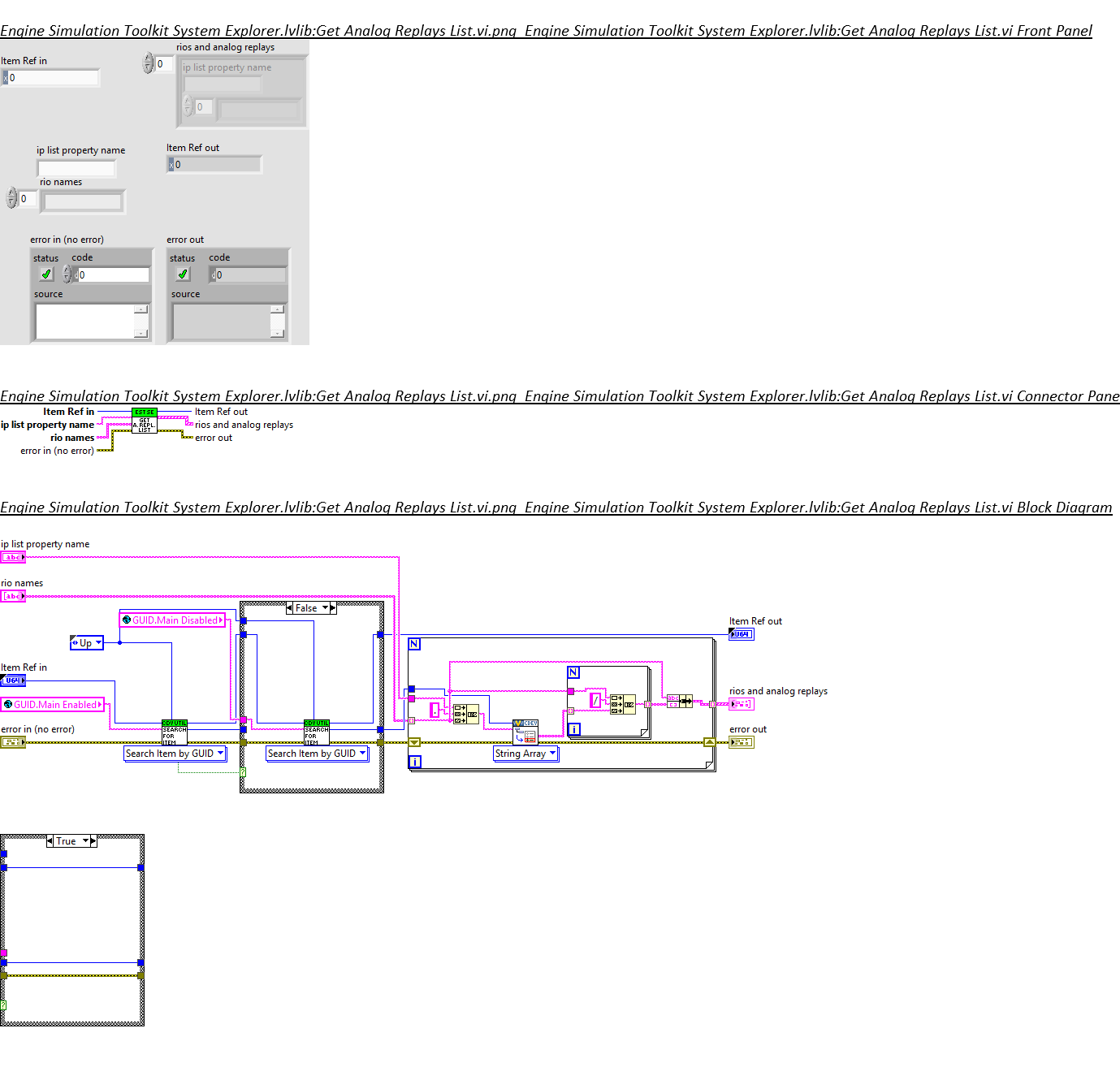

Engine Simulation Toolkit System Explorer.lvlib--Get Analog Replays List.vi.png:

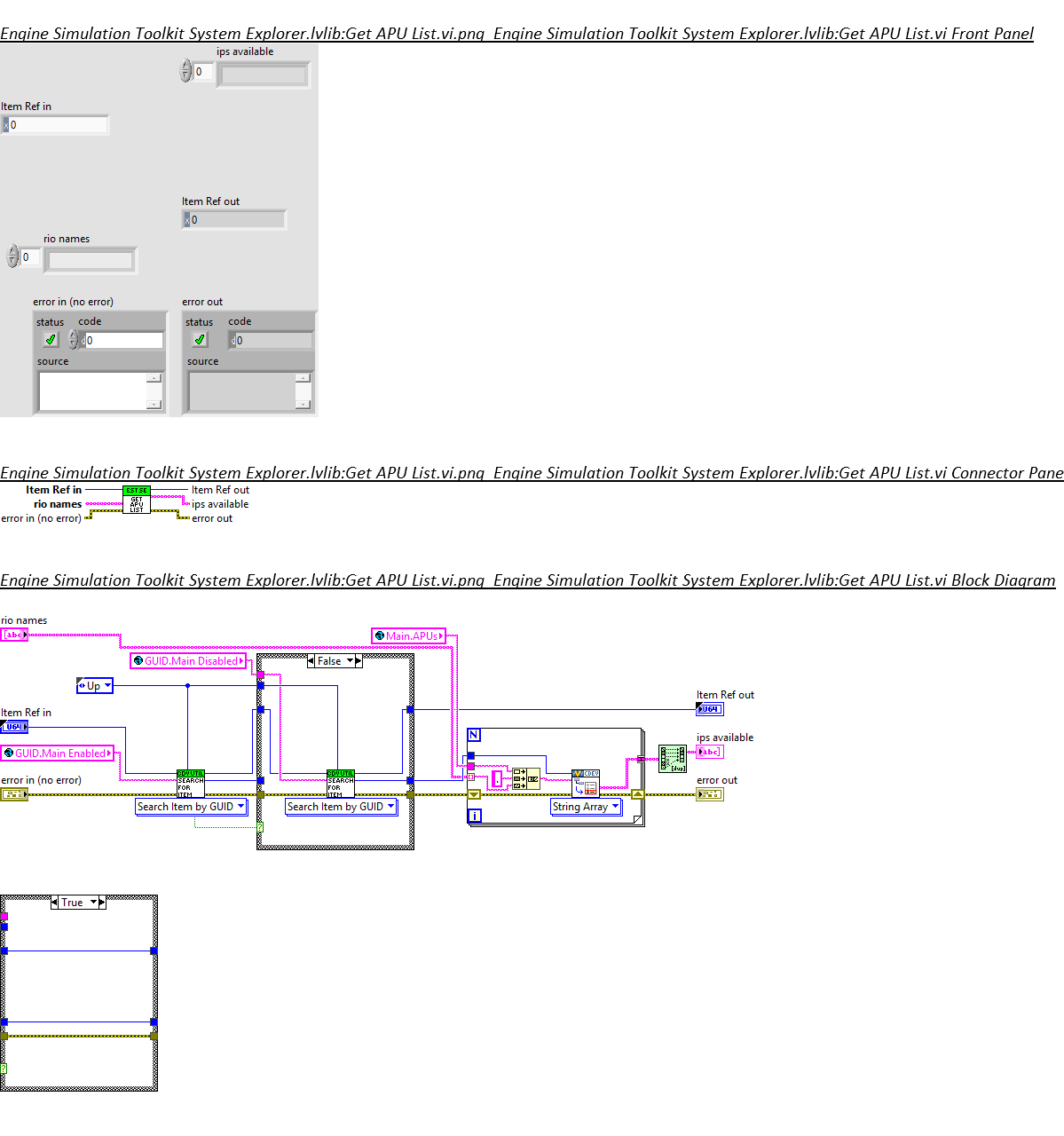

Engine Simulation Toolkit System Explorer.lvlib--Get APU List.vi.png:

Engine Simulation Toolkit System Explorer.lvlib--Get Bitfile Property Name.vi.png:

Engine Simulation Toolkit System Explorer.lvlib--Get RIO and Analog Replay Strings.vi.png:

Engine Simulation Toolkit System Explorer.lvlib--Get RIOs for APU.vi.png:

Engine Simulation Toolkit System Explorer.lvlib--Main Page - Multi FPGA.vi.png:

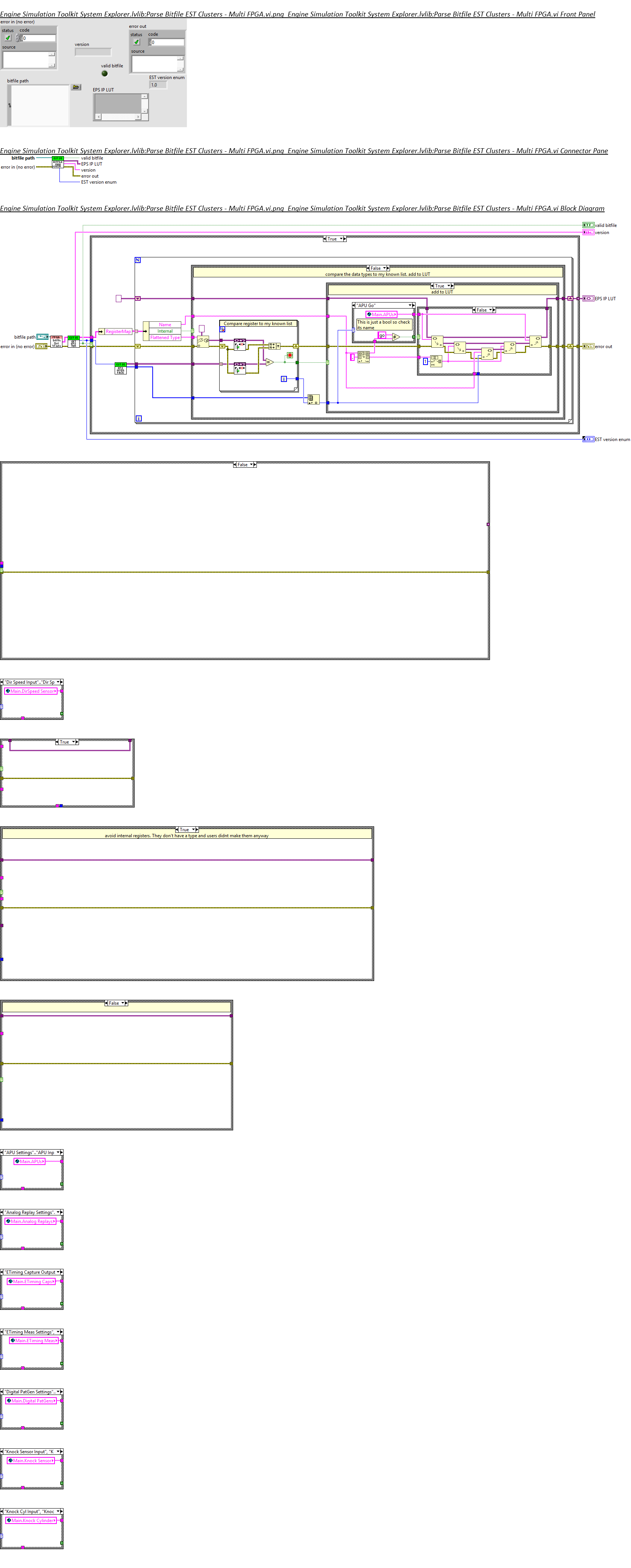

Engine Simulation Toolkit System Explorer.lvlib--Parse Bitfile EST Clusters - Multi FPGA.vi.png:

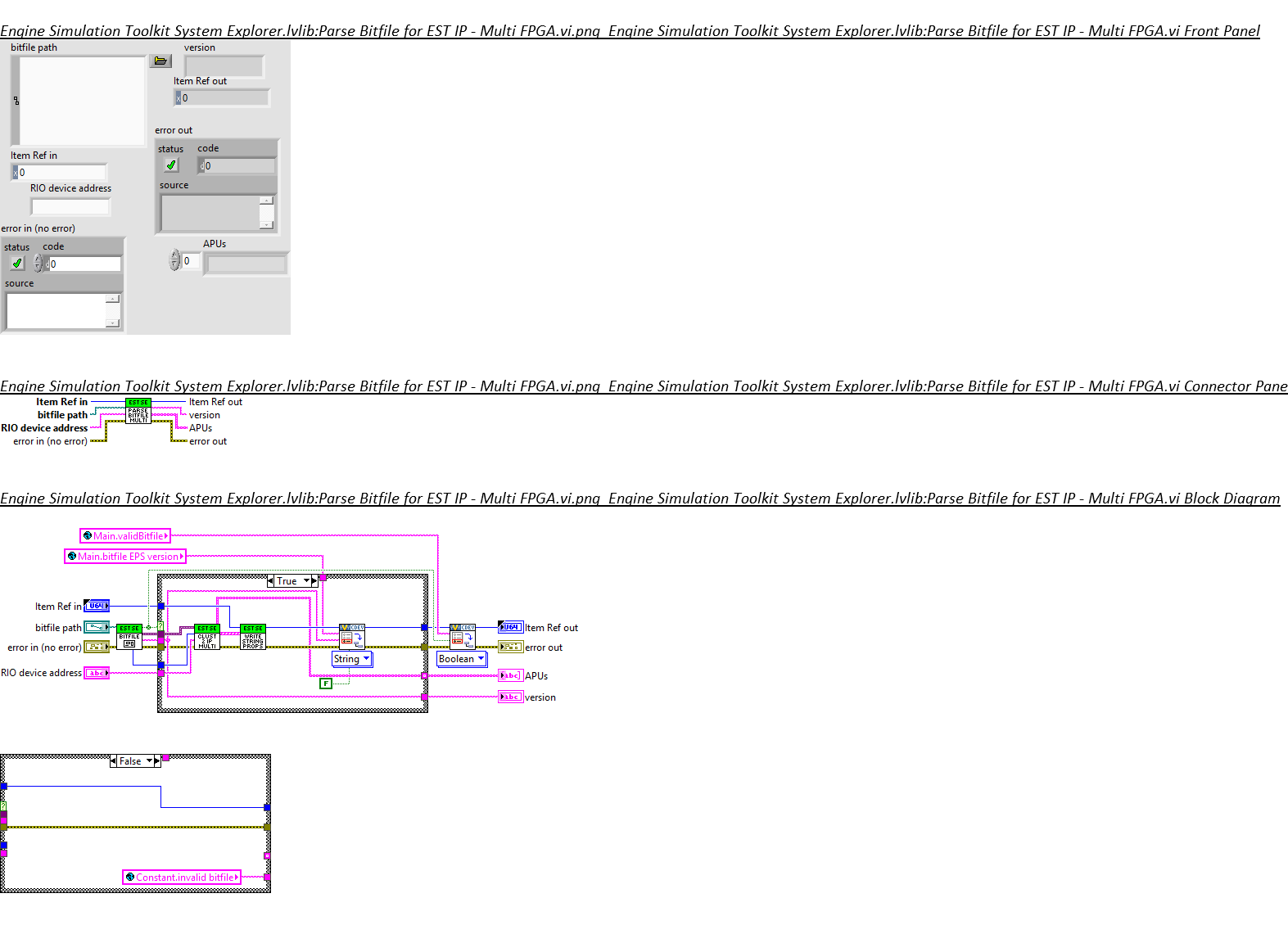

Engine Simulation Toolkit System Explorer.lvlib--Parse Bitfile for EST IP - Multi FPGA.vi.png:

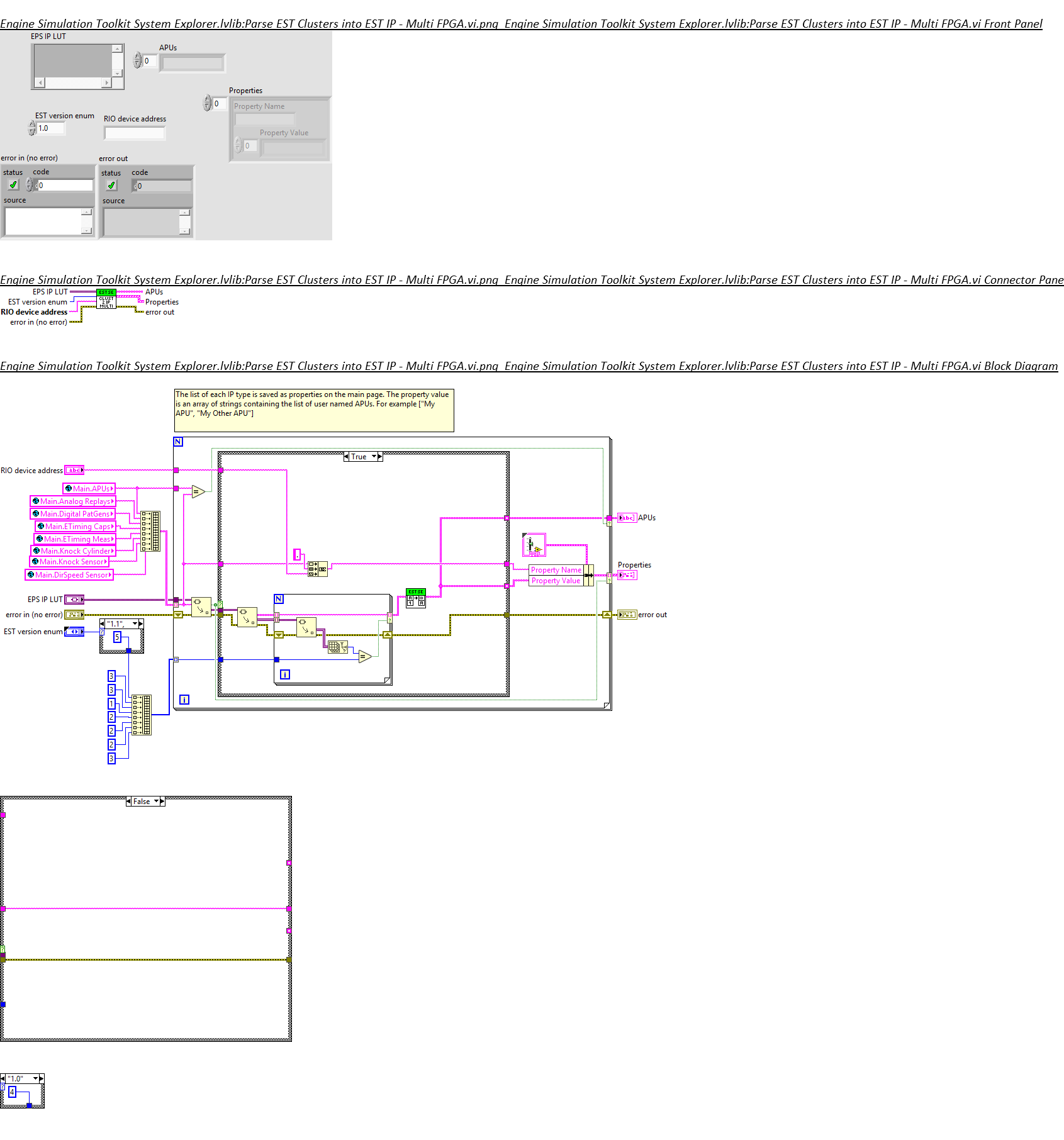

Engine Simulation Toolkit System Explorer.lvlib--Parse EST Clusters into EST IP - Multi FPGA.vi.png:

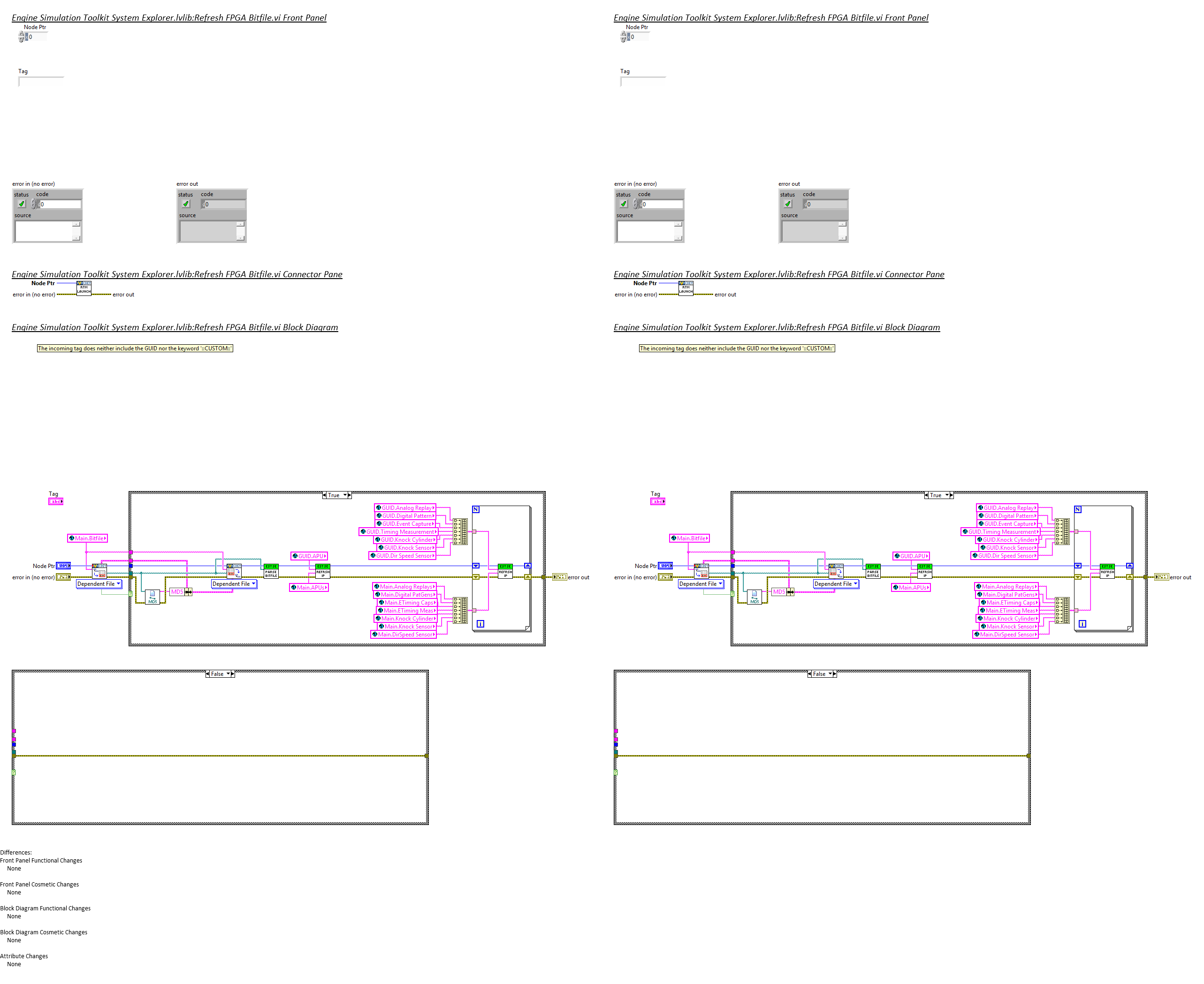

Engine Simulation Toolkit System Explorer.lvlib--Refresh FPGA Bitfile.vi.png:

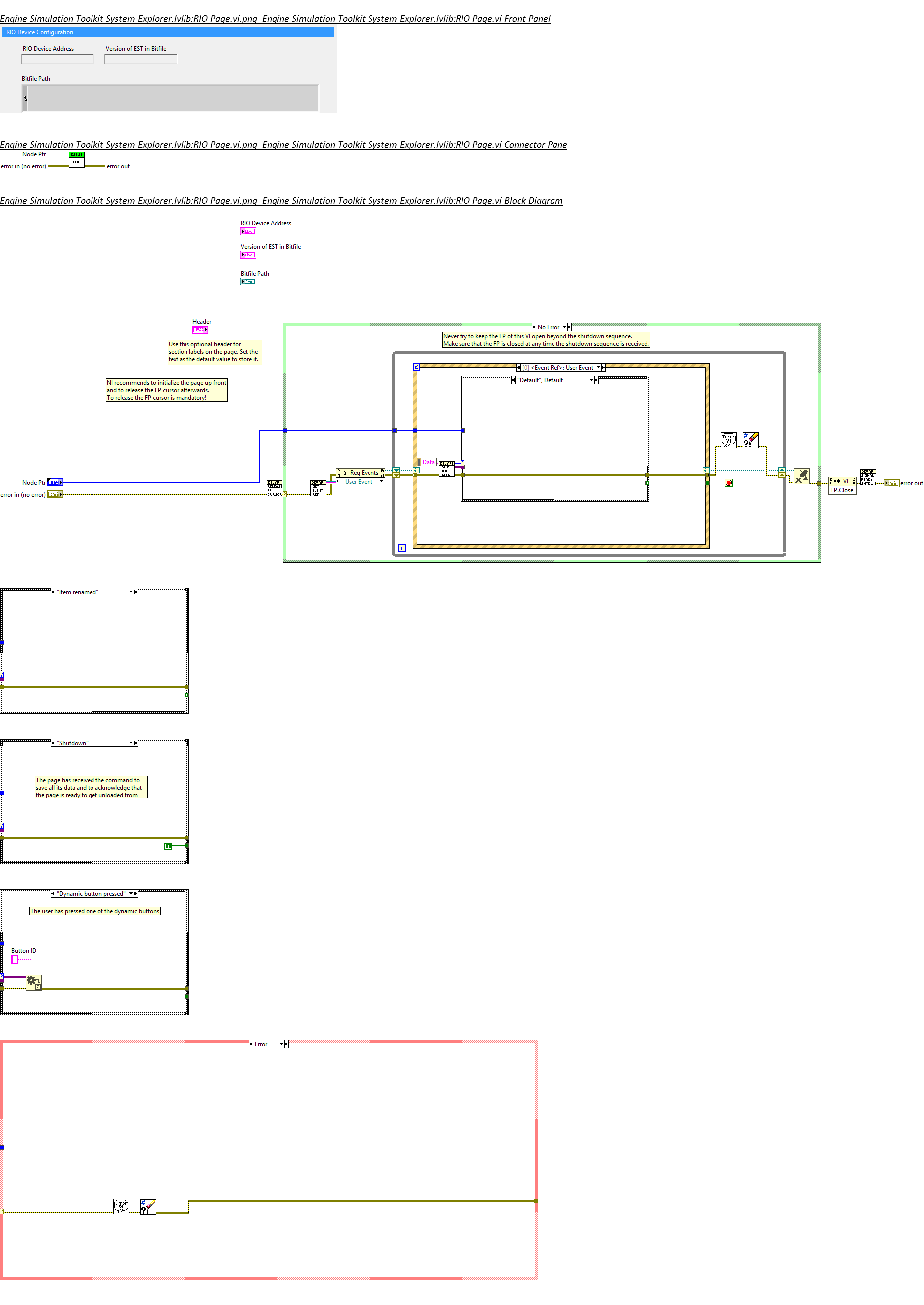

Engine Simulation Toolkit System Explorer.lvlib--RIO Page.vi.png:

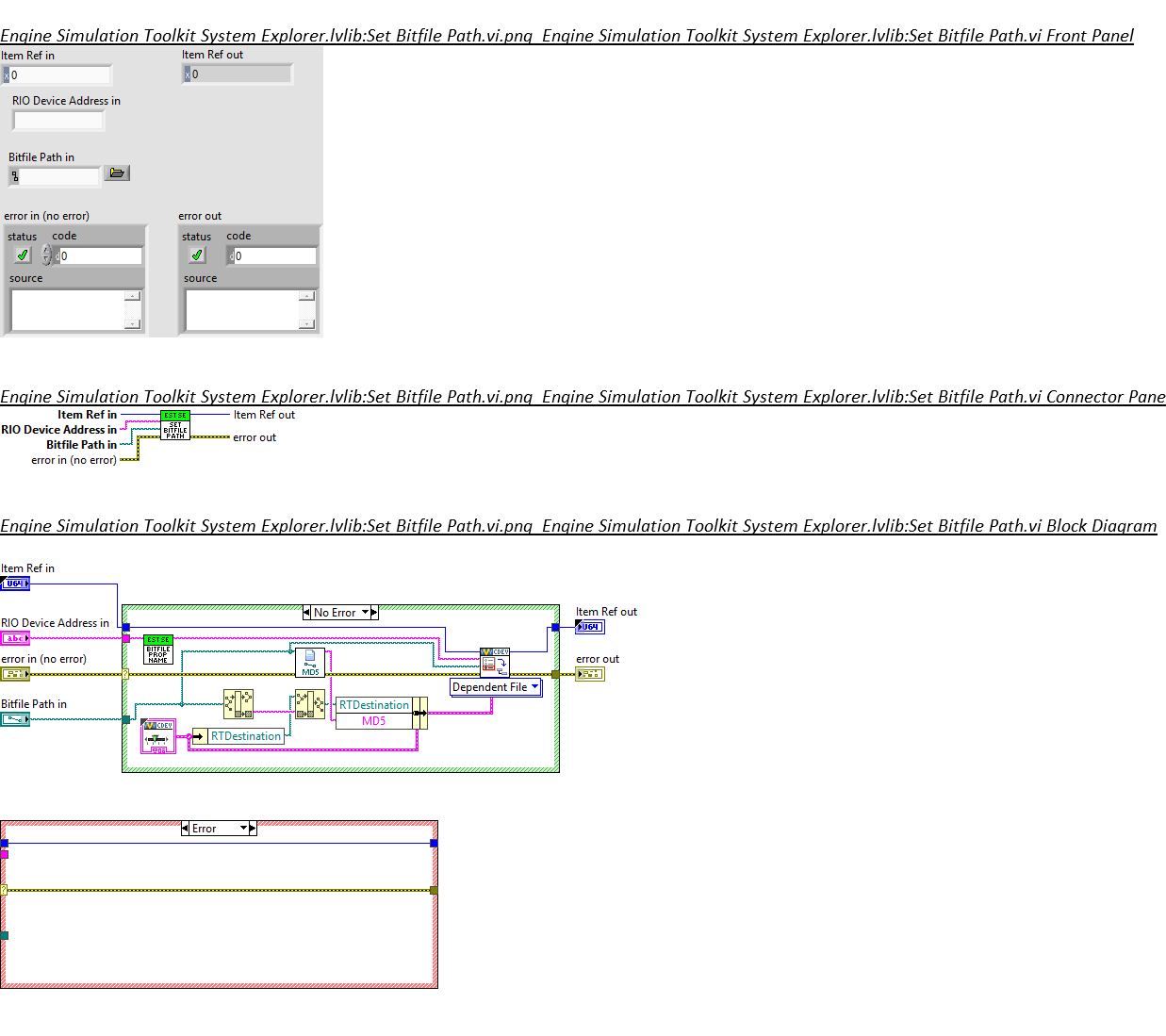

Engine Simulation Toolkit System Explorer.lvlib--Set Bitfile Path.vi.png:

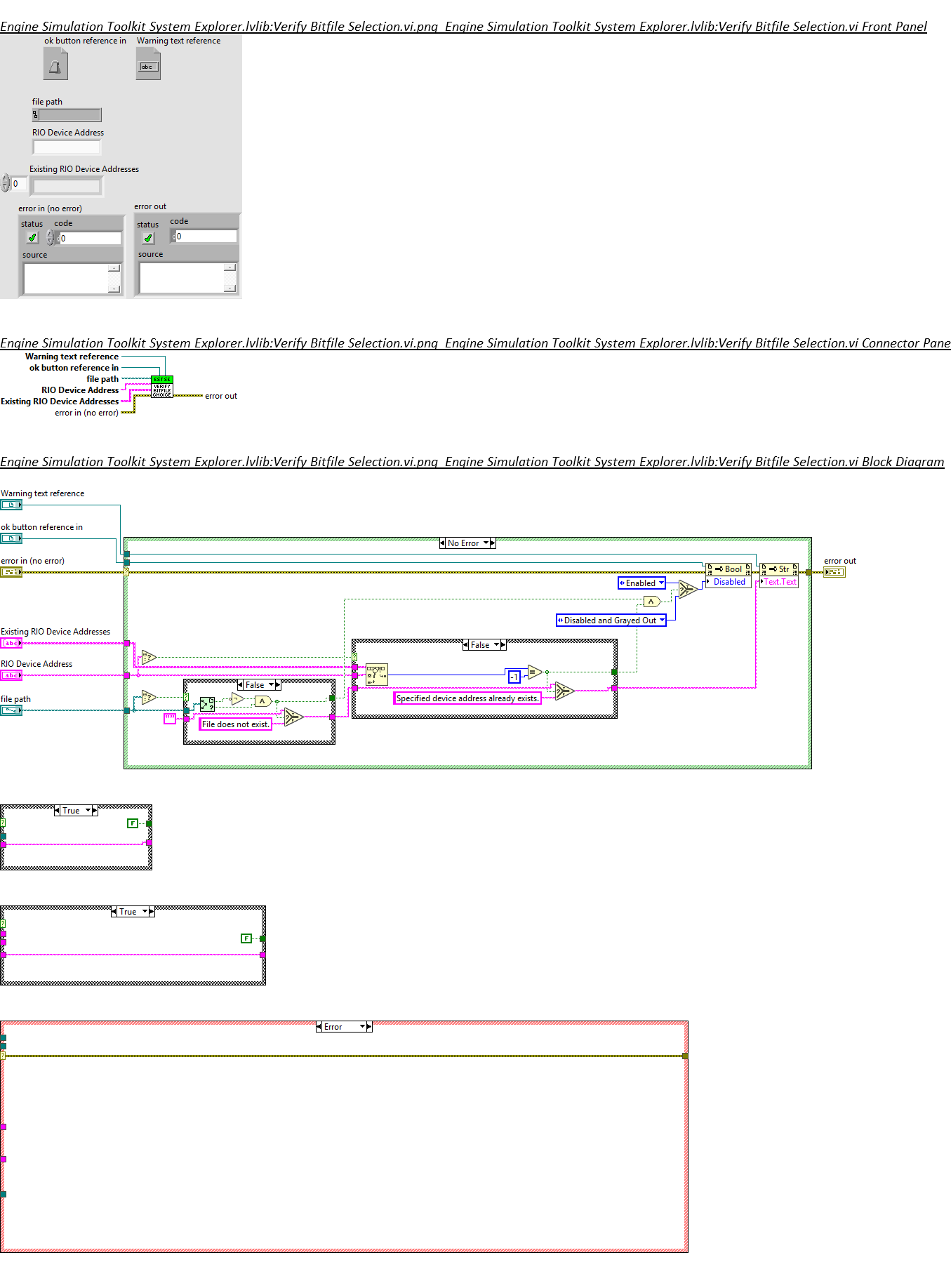

Engine Simulation Toolkit System Explorer.lvlib--Verify Bitfile Selection.vi.png:

The following VIs could not be diffed:

- C:\jenkins\workspace-toolkit-custom-device_PR-7-VK5VO5G7CW7GXSSJE5KIPL57RB4QANNIOIENHF63XZAVZBZ2FFAQ\Source\Shared\Constants and GUIDs.vi

- C:\jenkins\workspace-toolkit-custom-device_PR-7-VK5VO5G7CW7GXSSJE5KIPL57RB4QANNIOIENHF63XZAVZBZ2FFAQ\Source\Shared\Properties.vi

What does this Pull Request accomplish?

Add new pages for the main, APU, and Analog Replay sections of the custom device, based on the UI mock-up @buckd put together.

Why should this Pull Request be merged?

This provides a starting point to build the custom device engine and FPGA around; it is disabled by default and must be opted-into through a feature toggle.

My intent is to provide a useful platform for future development - there are several known issues listed at the bottom of this pull request which I feel do not prevent future work from being based on these changes.

What testing has been done?

Hand testing of the System Explorer portion of the custom device with the feature toggle enabled.

Configuring the custom device, adding multiple bitfiles, and adding analog replays all appear to work correctly from the System Explorer side.

Known Issues

Removing a bitfile/RIO does not remove the child elements from the System Explorer.The RIO device page is not populated with information