This reminds me of the glitches we saw when trying to do phase ramps on the AD9910. It was a few years back, so I forget the details, but IIRC:

- using the DDS in single-tone mode and only using profile 0

- then we were using the DDS in absolute phase mode, clearing the phase accumulator on each change of the phase (we had a phase accumulator on an FPGA that we programmed into the DDS via SPI, IO_UPDATE was synchronous with the DDS clock)

- stepping the DDS phase by as little as 1LSB would result in a very short glitch, before the DDS settled to the right value. This looked a lot like the waveforms you posted

- I tried a few things, like not using a synchronous IO_UPDATE, but wasn't able to get rid of these glitches. I tentatively concluded that updating the DDS phase while the RF was on/applied to the ion was a no-go.

- in that experiment we were able to get around this by using the ad9910 ramp generator to create our phase ramp. That didn't display these glitches, but is quite inflexible and a bit of a pain to use. This is one of the main drivers for the effort we've invested in having a proper artiq (S)AWG; personally, I wouldn't try to do any complex modulation with a DDS again unless I really had to

Anyway, not sure if this is related to your observations, but figured it might be a useful data point..

From @kjh-m on October 11, 2018 7:35

Hello,

I'm getting glitches from AD9912 output during a phase ramp experiment. Phase is ramped by small steps at a given intervals, while keeping the frequency set-point constant.

Problem persist for wide range of interval times (10 us - 10 ms) and frequencies (100 kHz to 300 MHz).

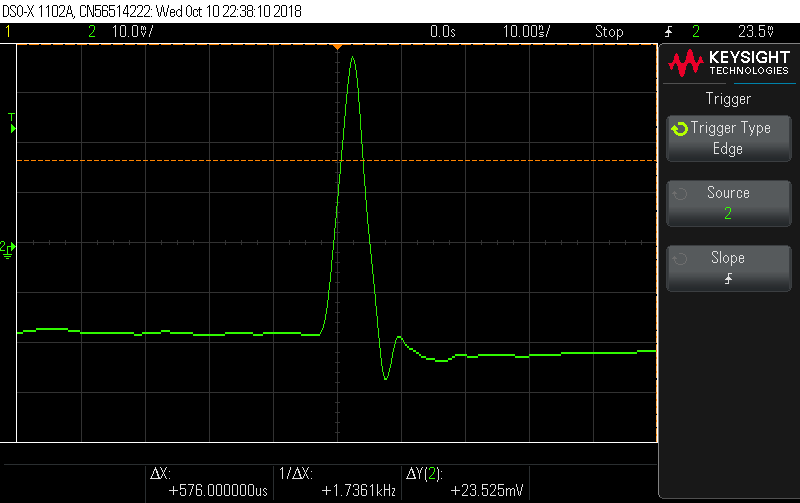

Initially I noticed this while doing frequency measurement with a counter. Observing the waveform with an oscilloscope revealed fast glitches occurring at random points of the cycle (see below).

Zooming in:

It seems that the glitches don't occur at every phase step. Screen capture of the oscilloscope shows glitch interval of 728 us, which is weirdly reproducible. In the measurement below, scope is triggered from glitches, so the waveform itself actually runs freely.

Also, DDS doesn't seem to lose coherence at the glitch, and the waveform continues smoothly.

All electrical connections are terminated to 50 ohms. Urukul is referenced to an external clock, while Kasli is not.

Simplified version of the phase ramping program is shown below.

Copied from original issue: sinara-hw/sinara#596